Hi,

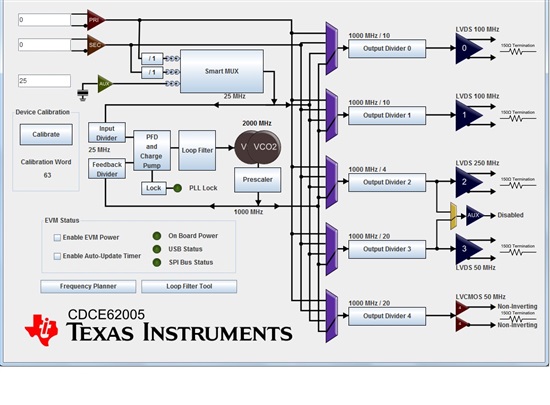

I used the “CDCE62005 Controller GUI v1.4.4" generate a register value. I only used an auxilary input crystal of 25MHz to get two 100MHz, one 250MHz and two 50MHz output

respectively. But I don't quite sure about the value I got from the GUI. Can you help me with these values? And how to configue the loop filter?

And the registers' value are as follows:

0 eb060330

1 eb060331

2 eb840302

3 eb0e0303

4 10e03f4

5 10007a55

6 6bff83e6

7 fdfffff7

8 fffffff8

PORTS

0 bf

1 ffffffff

2 ffffffff

3 ffffffff

INPUTS

PRI 0

SEC 0

AUX 25

EXTERNAL COMPONENTS

C4 1

R4 1

C5 1