Tool/software:

Hello,

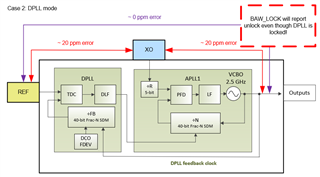

Based on the notes in TICS Pro (v1.7.7.10), I see recommendations to DISABLE the BAW Frequency Lock Detect when the DPLL is in use. Can you confirm that this is correct?

(I presume this is because when DPLL is active, it's responsible for the steering of the 2.5GHz BAW oscillator? And this means the BAW frequency lock detect is not needed for some reason?)

The reason for confusion is that the 1PPS default configuration has DPLL enabled, as well as the BAW Frequency Lock Detect. I had been assuming that this 1PPS default configuration is a safe/validated starting point for any design. It's concerning if this is not the case.

Thank you.