Tool/software:

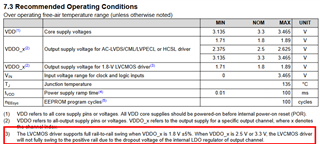

In VDDO_x where these are referred as output pins and it is told to connect to Output Supply (1.8, 2.5, or 3.3 V) for Clock Outputs 0 to 3 what does that mean, for application should i power these nodes to those supplies , are these 1.8,2.5,3.3 is the swing of the supply, If i have to connect these VDDO pins to those voltages should i generate them from different source and whats the current consumption, and what happens to the output if i connect to these different voltages?