Other Parts Discussed in Thread: LMK05318B, LMK5B12204

Tool/software:

I am looking to use the LMK05028. 3 outputs will be using the LVCMOS clocks and one will use the LVDS output clock. We will also be driving the PLL with 2 LVCMOS clocks and 1 LVDS clock.

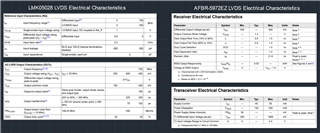

For the LVDS connections, does the VDDOx impact the electrical characteristics of the LVDS signal? I want to connect the following 2 components. I want to make sure I understand the Vpp and Vcm of the LVDS signals. I am supplying the VDDOx pin with 3.3V but would not like the Vpp to be that high.

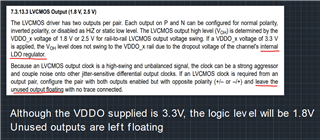

Similarly, I am supplying the LVCMOS pins with 3.3V. My understanding is the internal LDO will for the output to 1.8V logic level. Can the LDO handle having a 3.3V input for all my LVCMOS channels?