Tool/software:

Hello TI Team,

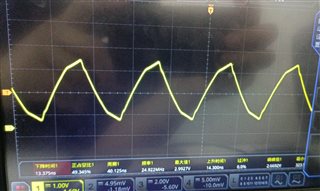

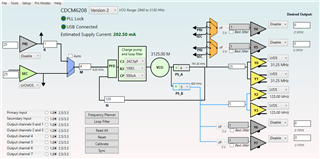

I'm working with the CDCM6208 in a clock distribution design, and I'm observing a strange behavior: the PLL intermittently locks and then unlocks repeatedly during operation. The PLL_UNLOCK pin toggles between high and low over time, indicating the PLL is entering and exiting the lock state in a loop.

Here are the details of my configuration:

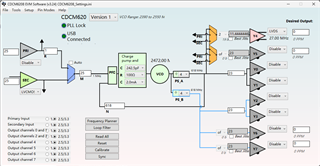

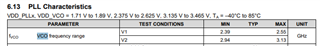

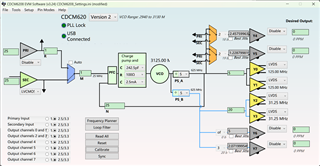

Register 0: 01B7 Register 1: 0060 Register 2: 02CD Register 3: 00F0 Register 4: 30AB Register 5: 0001 Register 6: 0016 Register 7: 0001 Register 8: 0016 Register 9: 0203 Register 10: 00A7 Register 11: 1C72 Register 12: 0001 Register 13: 0160 Register 14: 0000 Register 15: 0051 Register 16: 0160 Register 17: 0000 Register 18: 0051 Register 19: 0160 Register 20: 0000 Register 21: 0000 Register 40: 0000 Inputs: Primary Input Frequency: 25 Secondary Input Frequency: 25 Version 1 C1: 100p R2: 500 C2: 22n R3: 100 C3: 242.5p Charge Pump: 2m

STATUS0 :