Other Parts Discussed in Thread: LMK05318, LMK05318BEVM

Tool/software:

We are planning on using the LMK5B12204 network synchronizer in our design to synchronize two outputs. Before prototyping boards, we are trying to test the operation of the device using the LMK05318BEVM. We are under the impression that the only difference between the two chips is that the LMK05318 has 8 outputs and the LMK5B12204 has 4.

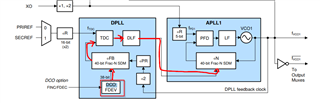

While testing, we are trying to utilize the DCO parameter to synchronize the outputs of two different EVMs. However, we notice that at a certain adjustment value, the chip loses the DPLL lock. We are trying to understand why this occurs. To me it appears that the DCO leads to slight shifts in the BAW VCO1 frequency. And that frequency is limited from 2499.750 MHz to 2500.250 MHz. So any DCO correction that puts the VCO1 outside of that range is invalid/not allowed. Is that the correct thought? If not, what else determines the max DCO adjustment?

Also, could you provide an explanation on how the DCO affects the output frequency? Does this adjustment change the numerator of the fractional N divider in the APLL1 or is it something else?

Please let me know if you need any other information and thanks for the help in advance!