Tool/software:

Hi TI

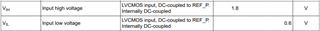

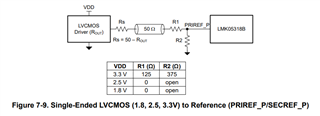

there is REFERENCE INPUT CHARACTERISTICS (PRIREF, SECREF) requirement in page 10 of datasheet, and the minimum recommended requirement of input slew rate is 0.5V/ns described at note (14).

Q1: if now the input voltage level is 1.8V, does that mean the rise time of 1.8V voltage level is equal to 1.8V/0.5V/ns=3.6ns?

Q2: does that mean the minimum rise time requirement of 1.8V voltage level for the input PRIREF/SECREF is 3.6ns, correctly?

<

| PARAMETER | TEST CONDITIONS | MIN TYP MAX | UNIT |

| dV/dt | Input slew rate(14) | 0.2 0.5 | V/ns |

(14) To meet the jitter performance listed in the subsequent sections of this data sheet, the minimum recommended slew rate for all

input clocks is 0.5V/ns. Phase noise performance begins to degrade as the clock input slew rate is reduced. However, the device

functions at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) are

less susceptible to degradation in phase noise performance at lower slew rates due to the common mode noise rejection. TI also

recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device

outputs.

>