Other Parts Discussed in Thread: CDCI6214,

Tool/software:

Hi team,

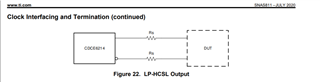

We thought to use CDCE6214RGET part in our design for PCIE gen 3 or Gen 4 application,CDCE6214 will support LP-HCSL output clock technique.

In CDCE6214RGET data sheet not mentioned the RS termination resistor value.

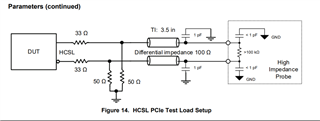

We have one more device for PCIE gen 3 support CDCI6214 part but this is not recommend for the new design.

But in that data sheet termination resistance values are mentioned for PCIE Test Load setup.

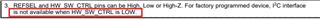

Can you provide the Termination details for PCIE Test Load setup for CDCE6214RGET (LP-HCSL), and CDCE6214RGET part will have two EEPROM page (0,1), we are going to use EEPROM PAGE 0 in our design.

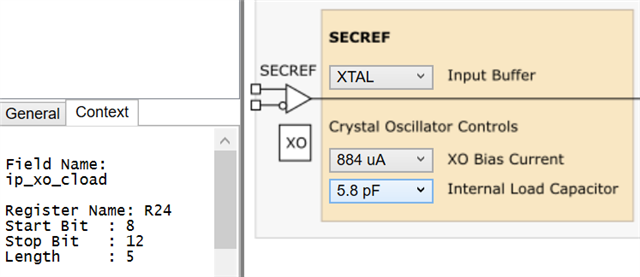

Which is factory program value will reflect on output. We want to know in EEPROM PAGE 0 default factory program frequency value?