Tool/software:

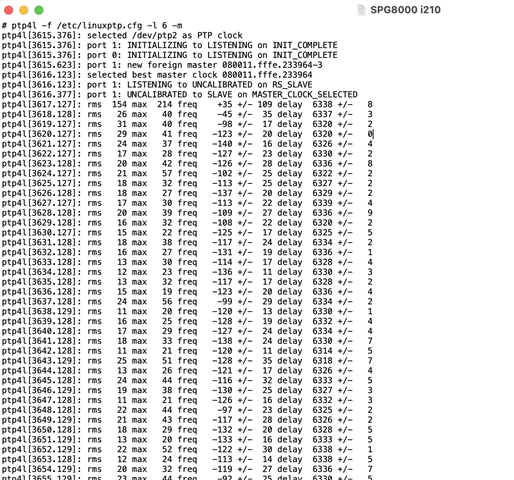

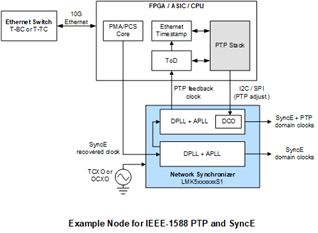

I am currently trying to synchronize the PTP clock output from an Aes67 audio device using Intel i210. The reference clock output from i210 is then filtered/multiplied by LMK05318B to output an I2S clock to downstream devices.

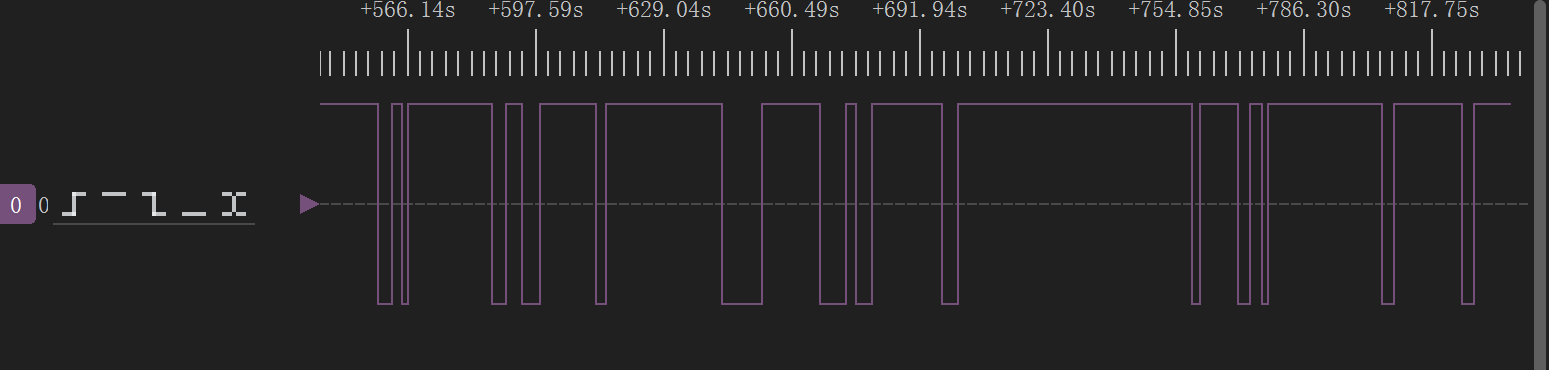

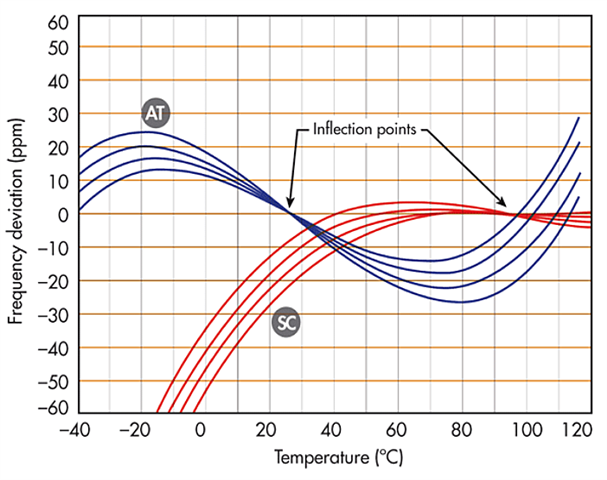

The i210 is controlled by an x86 Linux PC and synchronizes the external clock through Linux's PTP4L. The testPTP program controls the i210's SDP pin to output a 2KHz square wave signal as the reference clock for LMK05318B. The XO crystal oscillator of LMK05318B is a 12.288M TCXO

The PCB used for testing was drawn by myself, and the register configuration currently used for testing is as follows: