Tool/software:

Hi Team,

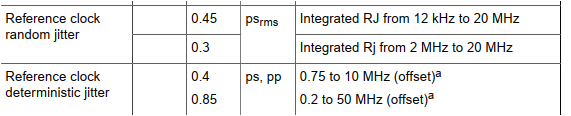

For LMK6H, lots of jitter measurement result are listed in datasheet for HCSL (100 MHz) type LKM6H device.

I am just curious if different package (DLE ann DLF) and different VDD(in associated with different VOH) will make the jitter result different? Do you have detail test condition to share?