Tool/software:

Hi,

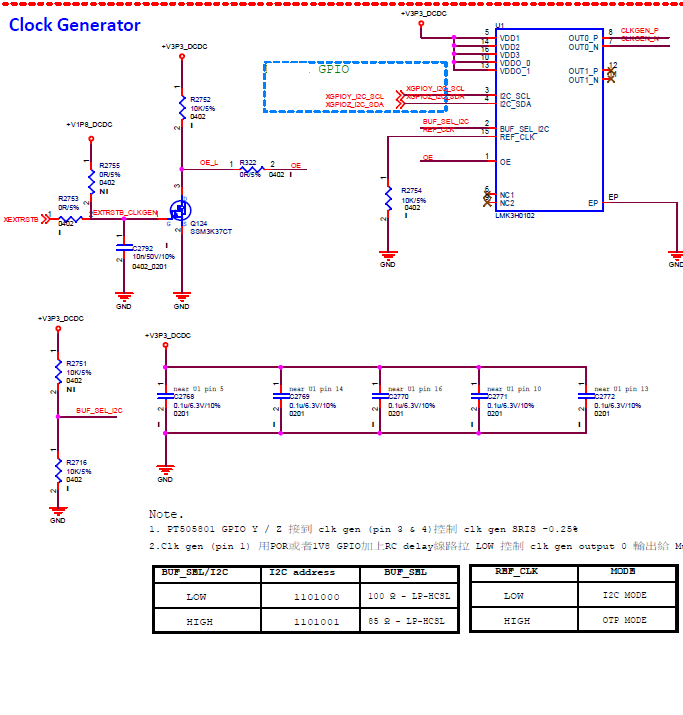

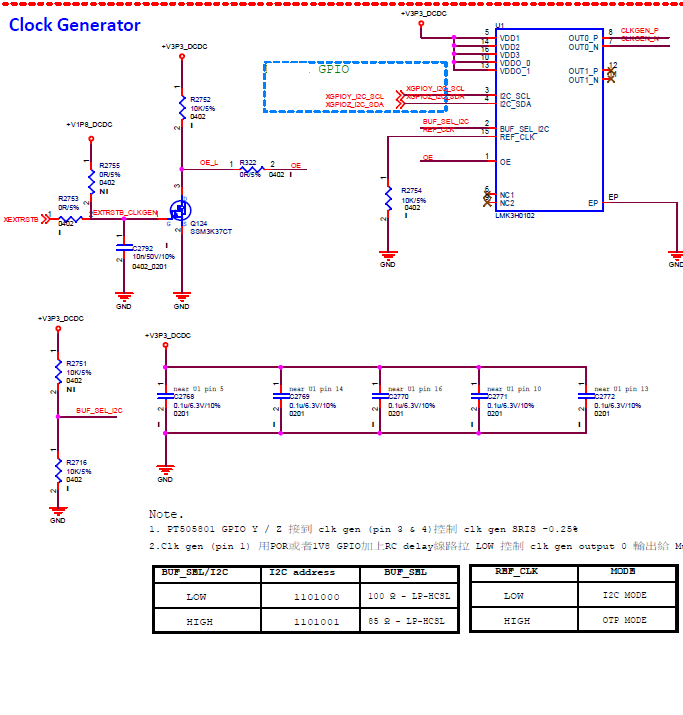

Would you please help review below LMK3H0102 schematic. thank you.

Thanks!

Jeff

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

Would you please help review below LMK3H0102 schematic. thank you.

Thanks!

Jeff

Hi,

Another question,

OE# (Pin 1): The reference design uses a 3.9kΩ pull-down resistor to ground. Since this value is quite specific, we would like to ask what the internal pull-down resistance is. Can it be changed from 3.9kΩ to 10kΩ?

Thanks!

Jeff,

Ferrite beads should be used to isolate the VDD and VDDO supplies for best noise performance.

Pin 1 has an internal 75k pull-down resistor. Using 10k externally is not an issue.

Thanks,

Kadeem

Hi Kadeem,

Curious about the reason why Pin6/Pin9 (NC pins) have output — would reserving test points for these two pins be helpful for debugging?

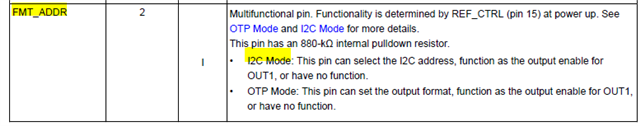

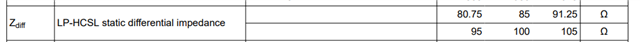

If IC2 Mode is selected (REF_CTRL pulled down), what is the default output impedance of the CLK GEN after power-on but before I2C communication starts? Is it 100 ohms? 85 ohms? What is the impedance tolerance? e.g., ±5%

Jeff,

These two pins (Pins 6 and 9) have no function, and can be pulled low, pulled high, or left floating.

If I2C mode is selected, the default impedance is 100-Ohm LP-HCSL. The tolerance is specified here:

Thanks,

Kadeem