Other Parts Discussed in Thread: LMK05318B, , LMK5C23208A, LMK5B12212

Tool/software:

Hello,

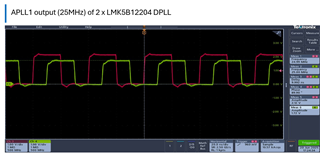

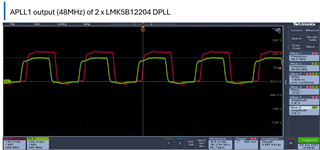

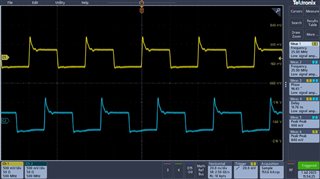

We are using mentioned DPLL part as clock generator to generate different frequencies from APLL1 and APLL2 output. APLL1 will be 48 MHz and APLL2 will be 25 MHz.

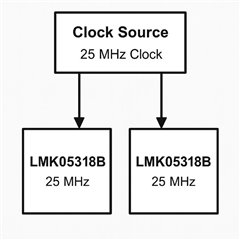

Requirement is that we will have multiple DPLL chips each generating above mentioned frequencies with synchronization. There will be 25MHz or 125MHz clock connected to PRIREF input of DPLL and 25 MHz oscillator to XO input. We require that multiple DPLL APPL1 output should be synchronized with each other and similarly for APLL2.

Please let us know if this is achievable / feasible with this part?

Also, is there any way to fix the phase delay of APLL1 and APLL2 output with PRIREF input clock?

Thank you!