Other Parts Discussed in Thread: , AFE7900EVM

Tool/software:

Hello TI Team,

We are using LMK04828 in one of our design, we need to know the two things about oscillator input pins.

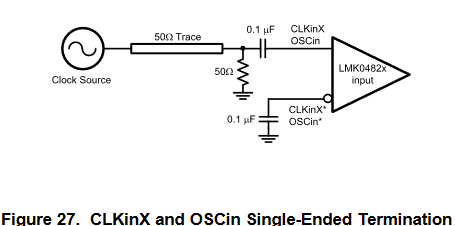

1. What is the maximum allowable input current on OSCINp and OSCINn pins for the single single ended clock input LVCMOS? For differential mode it is +/-5mA as per datasheet, for LVCMOS, how much it would be?

2. What is the input impedance on OSCINp and OSCINn?

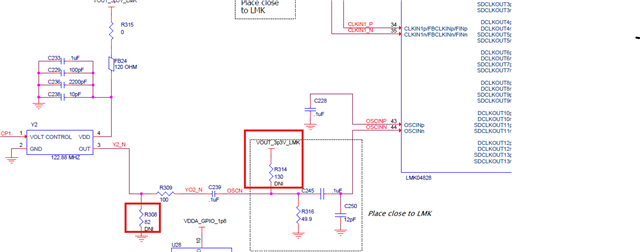

we are using the SiTime Oscillator, which is default operating at 3V3 supply with the passive circuit design we shall be making input clock logic level within acceptable limit of LMK i.e 0.2 ~ 2.4V as per datasheet.

For precise components selection we wish to know the above two points.