Other Parts Discussed in Thread: LMK05318

Tool/software:

Please see the attached file for detailed pictures.

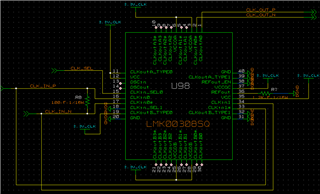

1. I would like to inquire about what happens to the CLOCK output (CLK_OUT_P, CLK_OUT_N) when the CLOCK input line is configured as shown below and input selection is made.

1)Apply the same CLOCK input signal (CLK_IN_P) to CLKin0 and CLKin1*

2)Apply the same CLOCK input signal (CLK_IN_N) to CLKin0* and CLKin1.

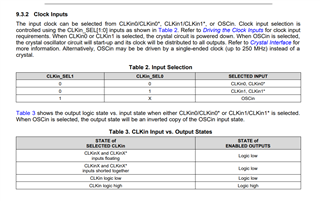

Question 1) What is the output signal when CLKin_SEL1=0 & CLKin_SEL0=0?

Question 2) What is the output signal when CLKin_SEL1=0 & CLKin_SEL0=1?

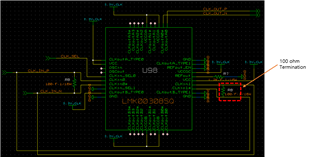

2. Under the same setup conditions as the previous question, what is the difference between having a 100 ohm termination between CLKin1 and CLKin1* and not?

3. Under the same setup conditions as the previous question, could you test it on EVKIT and let me know the results?