Tool/software:

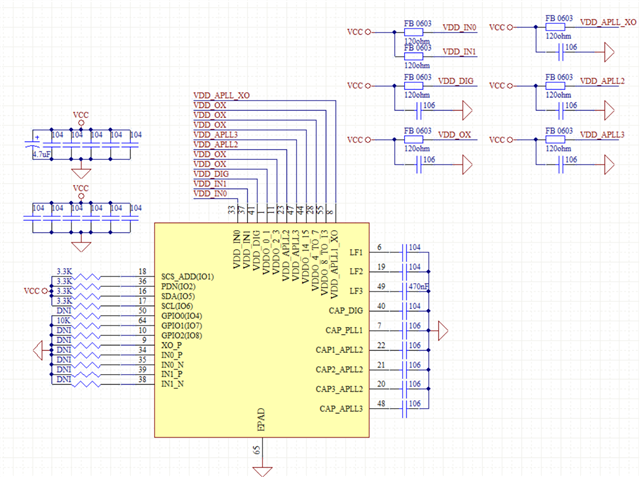

I am currently using I2C to communicate with the LMK5B33216 and have observed the following behavior:

-

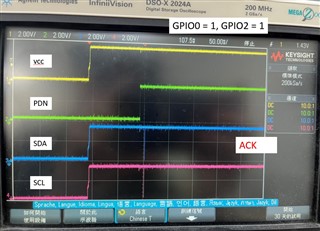

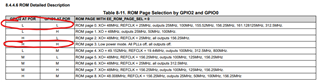

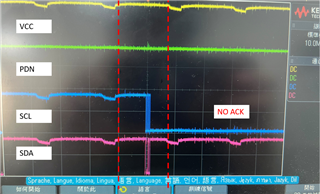

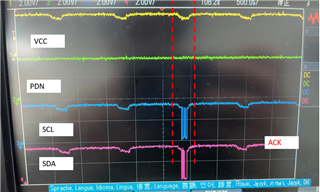

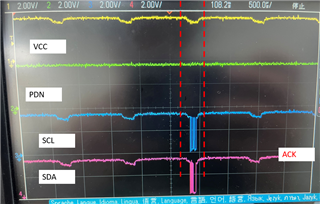

When GPIO0 = 1 and GPIO2 = 1, I2C communication works properly and the signals are stable.

-

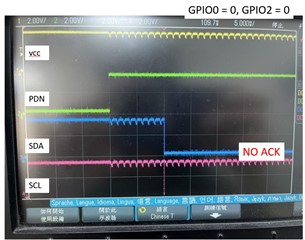

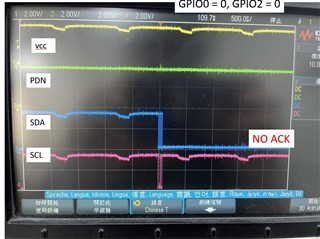

When GPIO0 = 0 and GPIO2 = 0, I2C communication becomes unstable (ACK is not received), and there is slight fluctuation on the VCC line.

Additionally, I noticed that during the fluctuation period, it is sometimes possible to receive an ACK when I2C signals are transmitted.

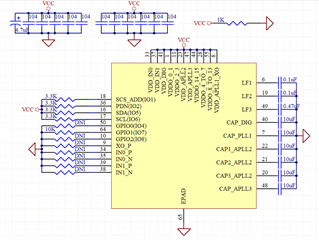

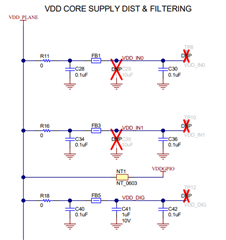

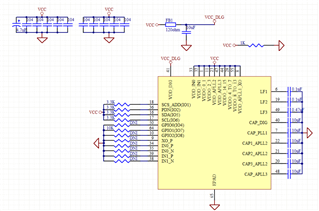

Below is my circuit diagram. I would like to know how to achieve stable I2C communication even when GPIO0 = 0 and GPIO2 = 0.