Other Parts Discussed in Thread: LMK3H0102, ALP, USB2ANY

Tool/software:

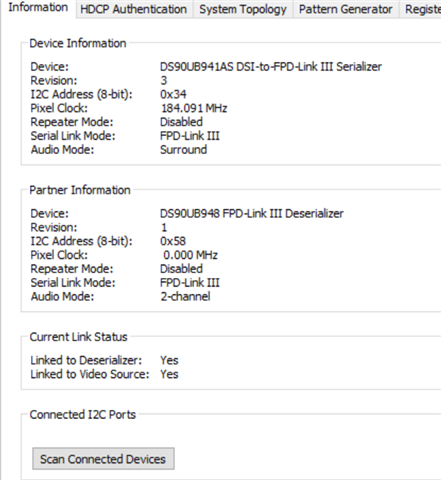

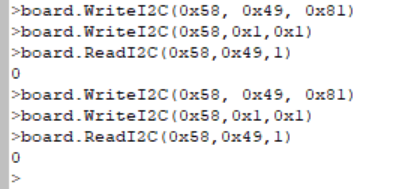

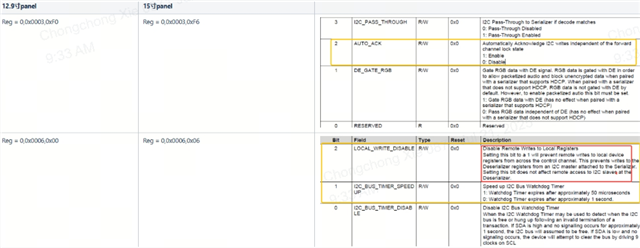

As mentioned above, the case submitted internally by TI is used for reference.

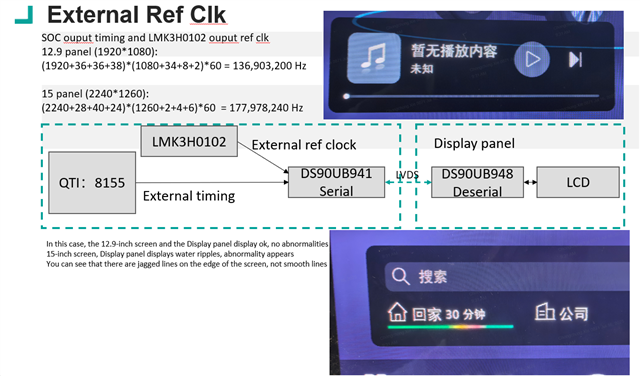

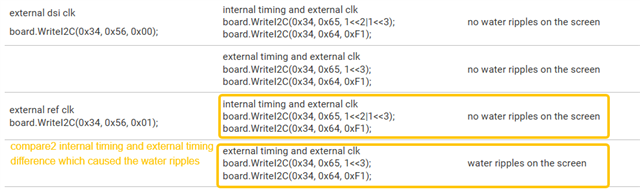

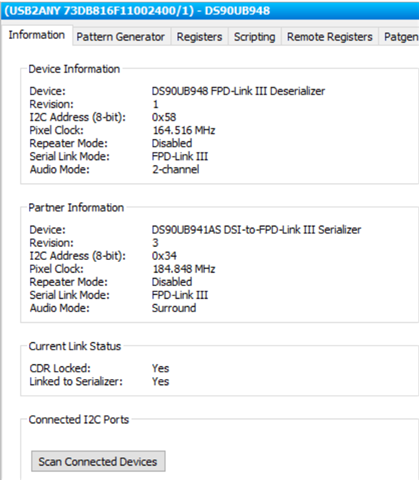

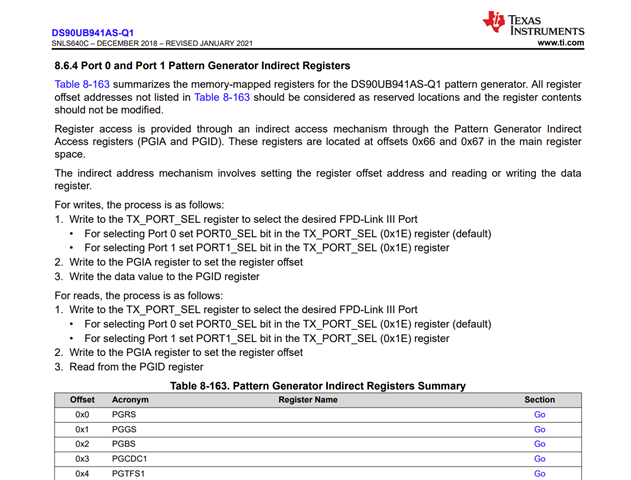

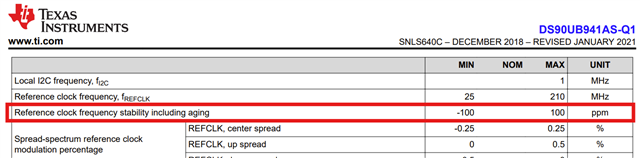

The LMK3H0102-Q1 chip output OUT0 is used to DS90UB941 as ref clk.

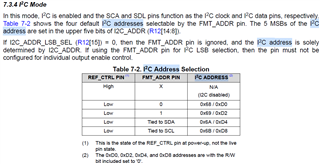

LMK3H0102 is currently the OTP code, but the REF_CTRL chip power-on is pulled up by default. At this time, it is OTP mode. Can I ask whether the chip I2C address can be read externally in this mode?

And how to read the chip address through I2C in OTP mode and then configure it to I2C mode.