Tool/software:

In ZDM mode i can calibrate phase offset but if there is some flag or interrupt that says this calibration has ended? I can't find any.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

In ZDM mode i can calibrate phase offset but if there is some flag or interrupt that says this calibration has ended? I can't find any.

Hi Piotr,

You can refer to the LOPL flag to see when the DPLL has reacquired phase lock with the newly applied phase offset.

Regards,

Jennifer

Hmm, now i am checking this and i see that writing to ZDM offset registers do not cause change i LOPL flag. It is always low. Also i continuously observed on scope that ZDM phase correct is working properly, i see that phase is change

Hello Piotr,

The LOPL register will live display the current state of the phase of the expected and actual values within our device.

When doing a phase adjust with ZDM there are two modes essentially. One mode is having the phase enable bit set which means if there is a change in phase you will begin to see the outputs shift at a set rate to the new desired phase. The other mode is while phase enable is not set in which the outputs instantly adjust to phase with the expected because there is not much phase difference between the current and final outputs. If the phase adjustment is very large you can get into an undetermined phase state of the outputs. If phase enable is turned off, after doing a phase adjust you must perform a soft-chip reset.

There are a few reasons why the LOPL may not be set.

Depending on the settings of the other parameters the phase offset register may just be shifting a very small amount of time. Depending on the validation setting that sets the LOPL bit the change applied to the ZDM offset may just not be large enough to get registered for a LOPL.

Another possible situation is that the device is not properly set to ZDM. The DPLL_PH_OFFSET register will actually still work if the device is not set in ZDM so you may be seeing this phase adjustment not in ZDM which would not trigger the LOPL register.

Every time you do a soft-chip reset does the phase of your output relative to your input signal remain the same?

Best Regards,

Kyle Yamabe

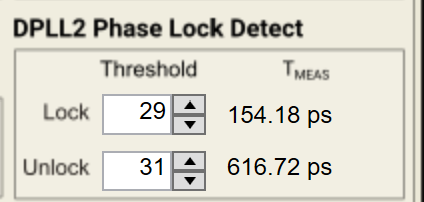

Yes and every time i shift signal by the same time ~40us. Here are my settings of phase lock detect?

Hello Piotr,

Are you able provide the tcs file of your configuration?

This will help me better evaluate the issue.

Best Regards,

Kyle Yamabe

Hello Piotr,

Which output are you trying to detect the LOPL signal for? I would assume OUT10 for DPLL3.

Looking at your configuration OUT4 is not enabled so ZDM will not be working for DPLL2 outputs.

Could you provide an image of the status page after clicking "soft-reset and sync" and then the "read status" button on the status page.

Best Regards,

Kyle Yamabe

Something is wrong with this file. It is OUT4 and ZDM is enabled for this output. I can not service LMK direclty by TICS but from my embedded app. Soft-reset is necessary? ZDM offset work alwayswhen write appriopriate registers. Also LOPL flag is not only for REFx inputs?

Hello Piotr,

I have continued testing your configuration and when I open it I get very strange results on your file.

If you are measuring from OUT4 the tcs file has OUT_4_EN as not enabled so there should be no outputs on the OUT4 channel so ZDM should not be working. I think it is possible that there is an error on our validation registers for REF2 and REF3 or some setting has become out of sync.

Are you able to change the inputs from REF2 and REF3 to REF0 and REF1? If that is ok for your design please try the attached configuration to test.Reference input changed and re-ran startpage configuration.tcs

The LOPL flags are for each of the DPLLs. But the loss of phase lock while the device is in ZDM is taken with respect to the input reference.

For programming the device in the register space, not just EEPROM a Soft-reset is necessary.

To perform a Soft-Reset you can program these registers after the rest of the registers have been programmed. This just asserts and de-asserts the SWRST bit to perform soft-reset.

0x001740

0x001700

Best Regards,

Kyle Yamabe