Part Number: LMK05318

Other Parts Discussed in Thread: DP83869HM, , LMK5B12212, LMK5B33414, LMK5B33216, , , AM625, AM6252

Tool/software:

HI TI Team,

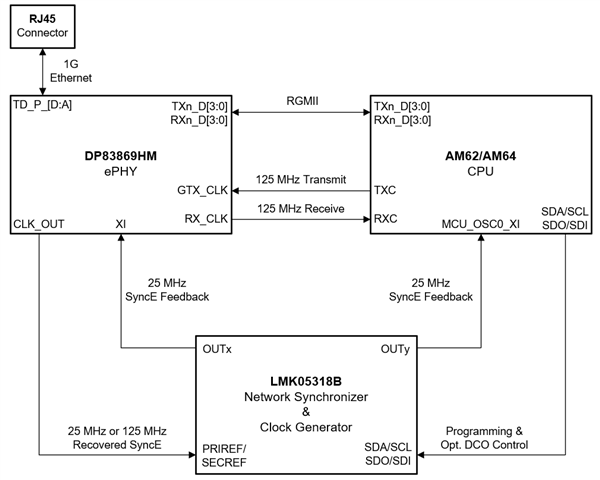

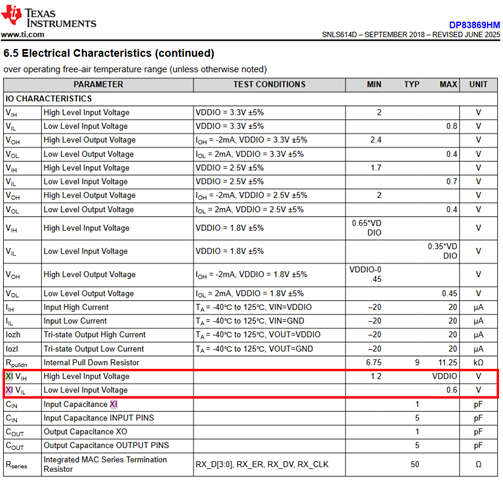

We are looking to interface the AM62x processor with the DP83869HM Ethernet PHY for a 1Gbps Ethernet connection. In addition to that, we want to add Sync E support to our system to connect multiple systems. For this purpose, we are looking to use the Network Synchronizer Clock LMK05318.

To achieve this and make the first time right design, we are looking for your support regarding the required Hardware connections of all three components altogether. I already referred to this link, but not able to get total clarity on how the connections will be done and communication will take place.

Could you please share the reference design of the Sync E implemented system, if available?

If not available, kindly guide us on how connections will be made.

Thanks & Regards,

Sahil Nayak