Tool/software:

Hello,

I have two LMX2572LP in my design and they work fine with VCO_PHASE_SYNC=1, and produce the correct frequencies.

After pulsing the SYNC pulse, we wait for each of these PLLs to lock, by checking the MUXout pin for lock detect for both.

Question1: is this an acceptable method, to check the MUXout lock detect pin? We do see this seems to work, but wanted to confirm.

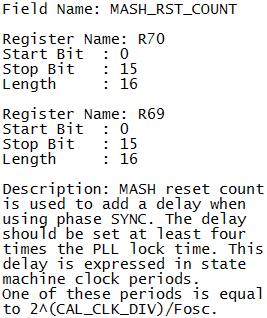

After an interval we do see this pin go high. Also confirmed that by changing MASH_RST_COUNT we can adjust the delay.

Question2: are both PLL's MUXout (lock detect pin) expected to go high simultaneously at exactly the point when phase sync has occured, or perhaps a fixed delay after phase sync has occurred?

Or can the two MUXout lock detect pins go high at different times?

This will help us determine if phase sync has actually occurred or not.

Thanks,

Arun