Other Parts Discussed in Thread: LMX2820, LMK61E2

Tool/software:

Hello,

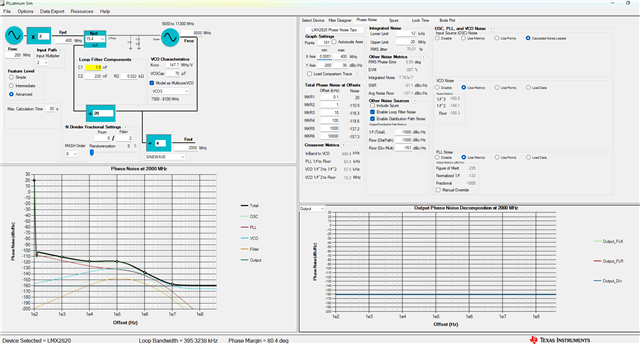

we have a custom board with the DAC38 running at 8 GHz and the ADC12J running at 4 G. It is working and stable.

The master clock is a 100 MHZ OCXO with good specs. It also feeds other boards with the LMX in the same system.

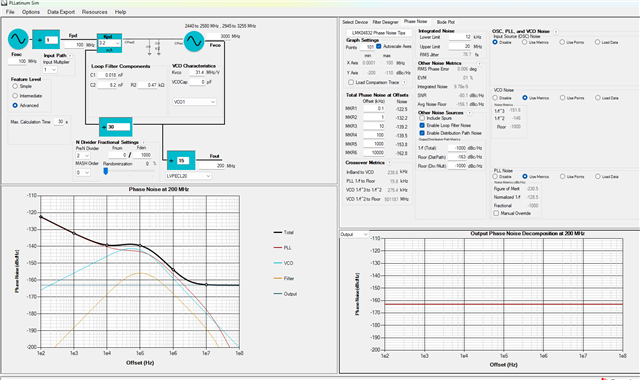

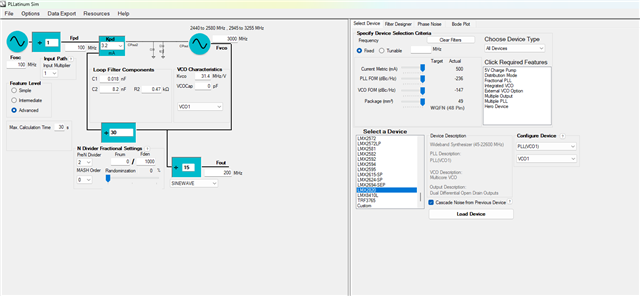

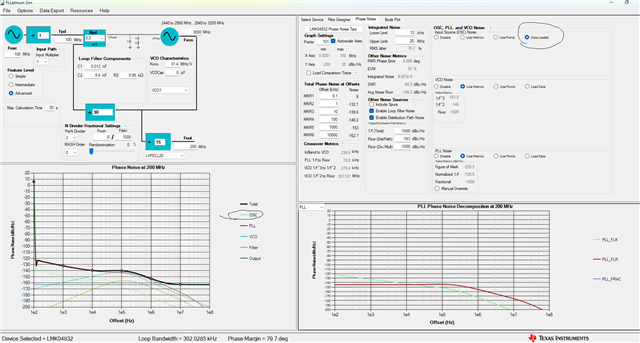

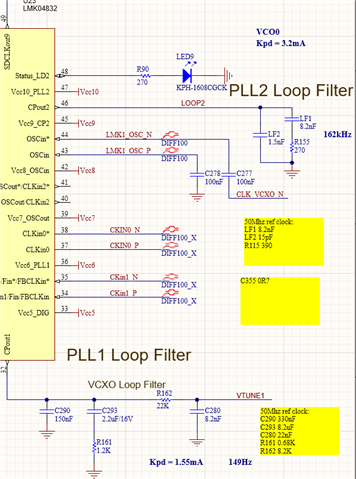

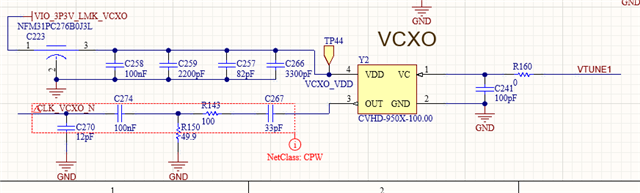

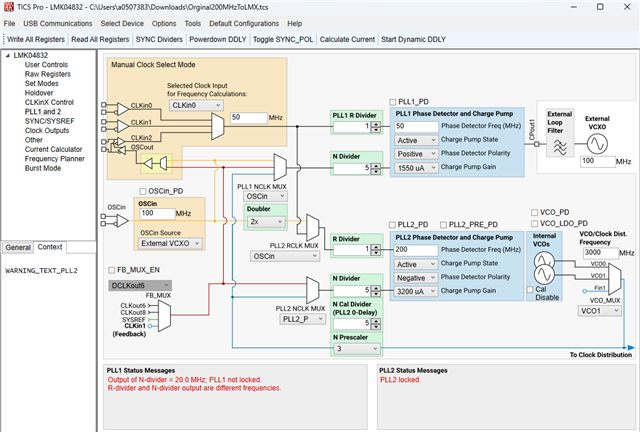

The master clock feeds the LMK which generates the SYSREF, 125 MHz for the JESD IP and a 200 MHz to the LMX.

Both chips are using internal VCO.

Now, we are not happy with the ADC's SNR and we have started looking into the clock, which we think could have too much jitter and possible too low level (It's only about 3.9dBm after BPF). The max output from the LMXs RFOUT is 6 dBm.

1, So, we placed the LMK in distribution mode with a 1G from a SMB100 generator. It seems that the clocks are OK, but while the DAC works but we loose sync on the ADC.

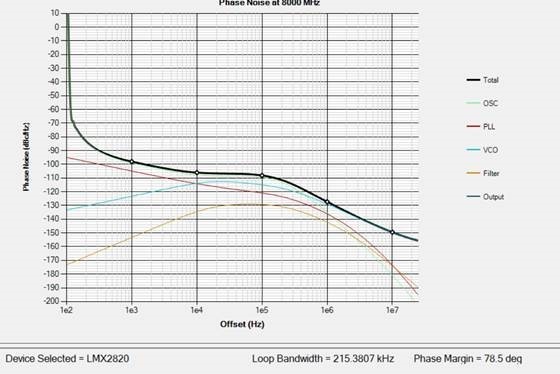

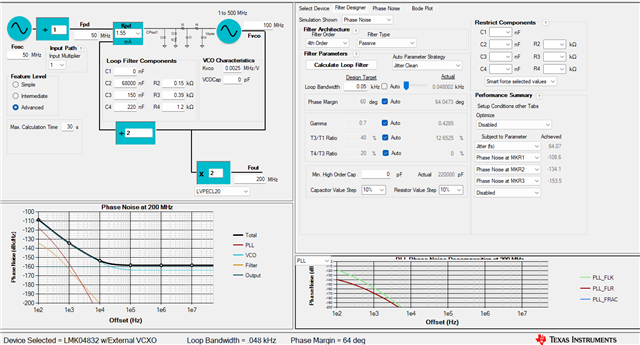

2, Then we changed the loop filter on the LMX only, tuning for jitter, (reverting back to original clock design) and the same thing happened. DAC is still running.

We cannot easily access the clock but we are designing a couple of pcbs that we can install in-circuit and we have acquired a scope fast enough to have a look.

But can you think of anything that can cause the above? It's a properly designed board, and we have already fielded quite a few of these.

Cheers,

G