Other Parts Discussed in Thread: , TLC3555-Q1, TLC3555

Tool/software:

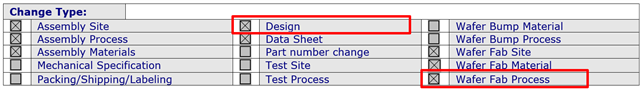

PCN 20231130002.1 is the “Qualification of RFAB using qualified Process Technology, Die Revision, Datasheet update and additional Assembly Site/BOM options for select devices”. Devices affected are TLC555C, TLC555I, TLC555Q, but not TLC555-Q1.

What are the performance differences expected?