Tool/software:

Hi support team all.

My customer asked us some questions below.

We appreciate it if you could answer our questions.

Q1:

Is it possible to output RFout B = RFout A / 3?

Example settings are as follows:

RFOUTA = 12.525 MHz

RFOUTB = 4.175 MHz

If this is possible, could you please tell me the settings?

Q2:

If dividing by 3 is not possible with Q1, it seems that harmonics of the set frequency are output from RFout B. Therefore, I am thinking of setting it to divide by 6 (extracting the RFout A / 6 component) and adding an external filter to extract twice the component of RFout B.

However, are there any concerns about device operation when using this method? For example, if I add a band-pass filter to RFout B and extract RFout B x 2, could the fundamental component of RFout B be reflected by the filter, causing the level to become unstable?

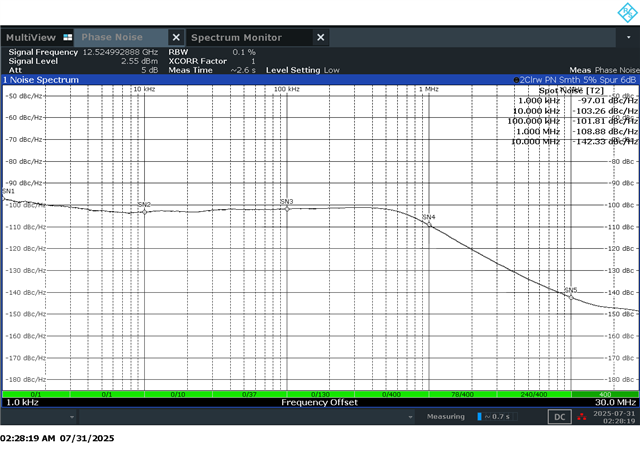

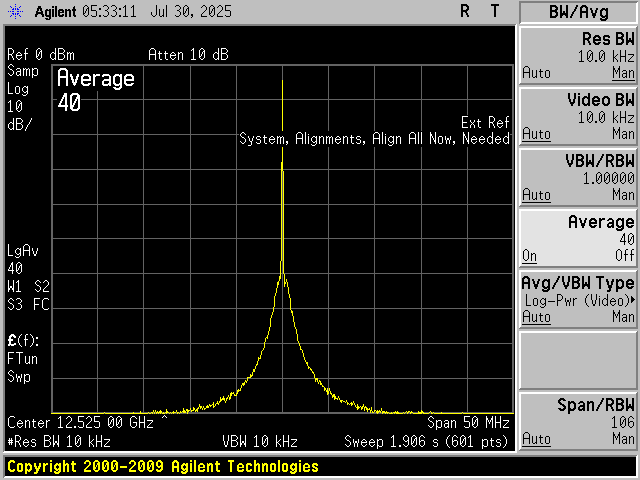

Q3:

The frequency I want to set is the setting for Q1. (There are three other settings.)

Since the reference signal Fosc is planned to be 25 MHz, I think I will have to set it to fractional, but I would like to know the recommended register settings to operate it under optimal conditions, such as minimum spurious, minimum phase noise, and maximum power output from RFout.

I would like to actually check this on an evaluation board, so it would be very helpful if you could tell me the settings in TICS Pro.

Best regards,

DH