Tool/software:

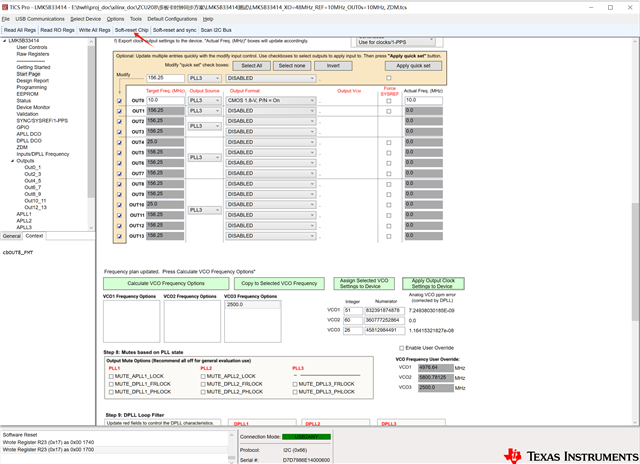

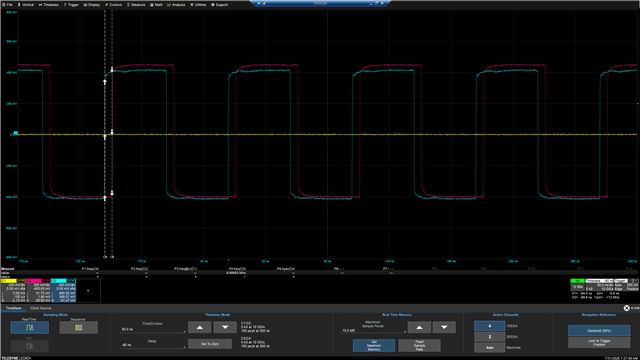

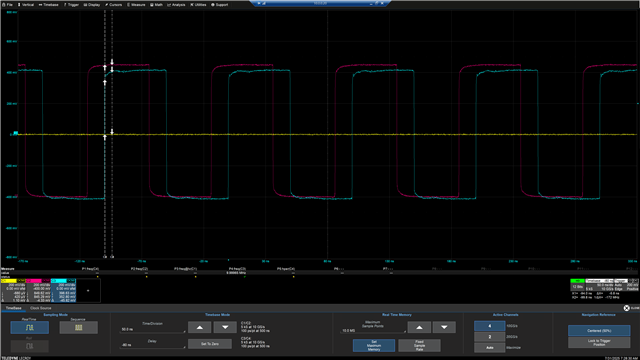

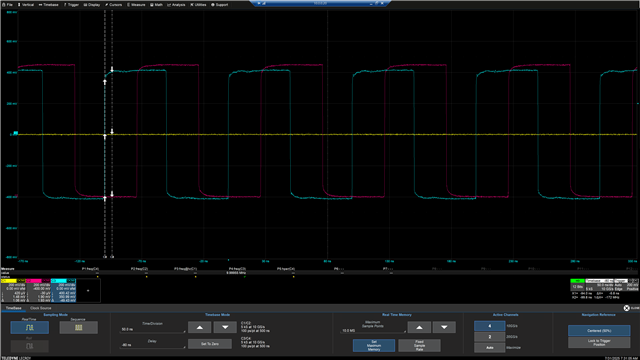

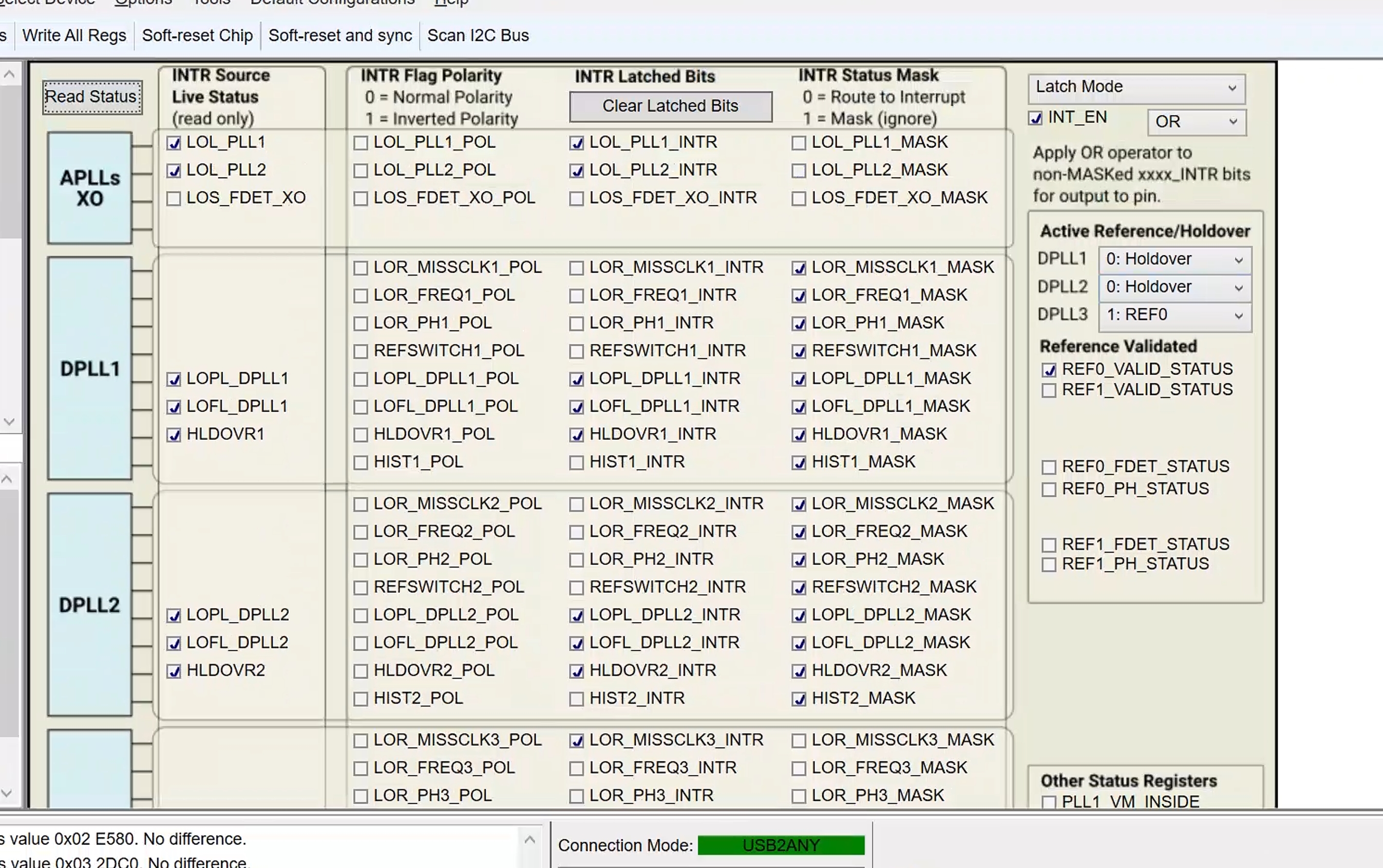

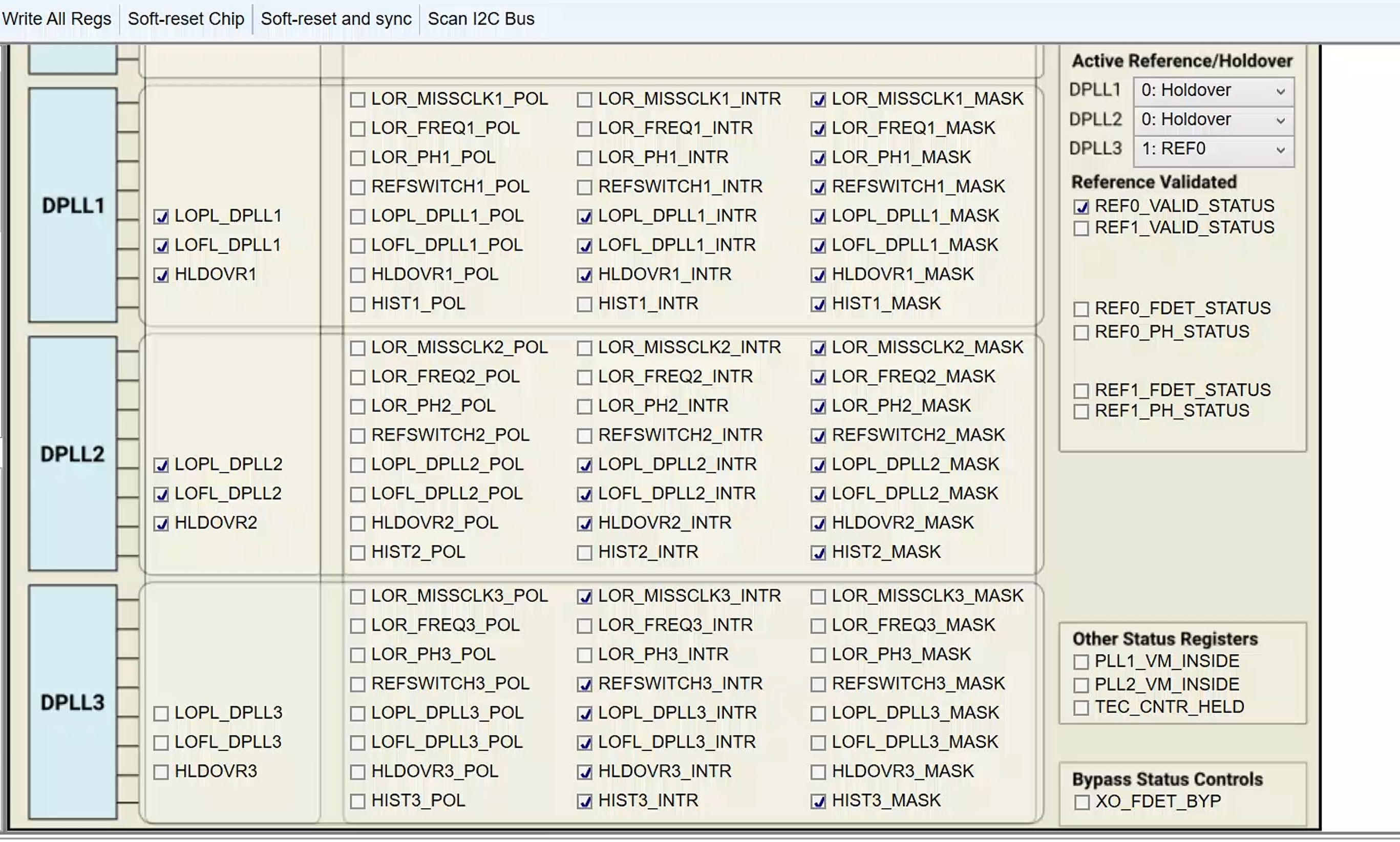

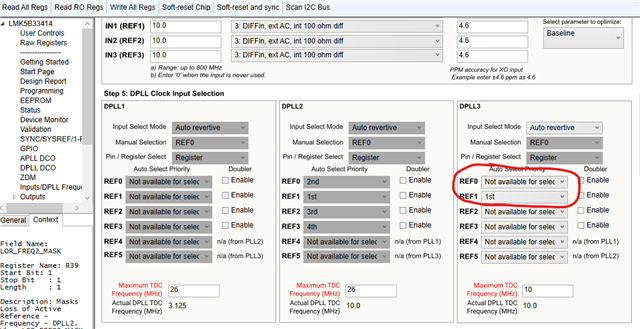

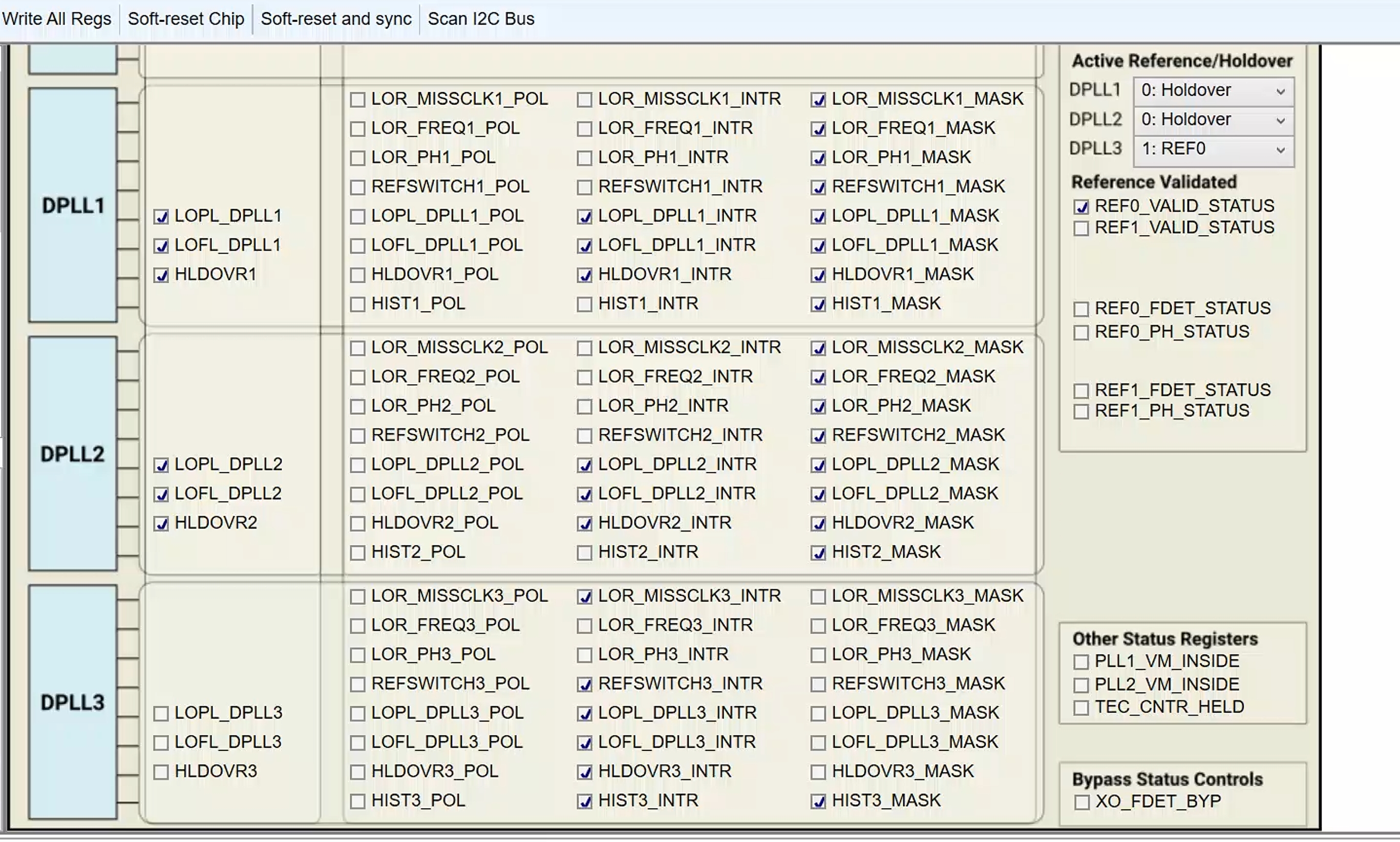

When I was testing the ZDM mode with a 10M reference input using LMK5B33414, I noticed that the phase of the reset chip was deviating. What could be the reason for this? The attachment contains my configuration file. The figure shows the phase difference between the output channel 0 of the software and the reference clock after several resets.