Other Parts Discussed in Thread: LMK04832, LMK04832-SP

Tool/software:

Hi,

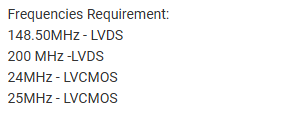

This is Dinesh from iWave Global. We are looking for space grade oscillators for our project. I came across the space grade oscillators in TI site. I need to confirm our frequencies requirement with you. Please confirm it.

Looking forward to the response.

Regards,

Dinesh