Tool/software:

All,

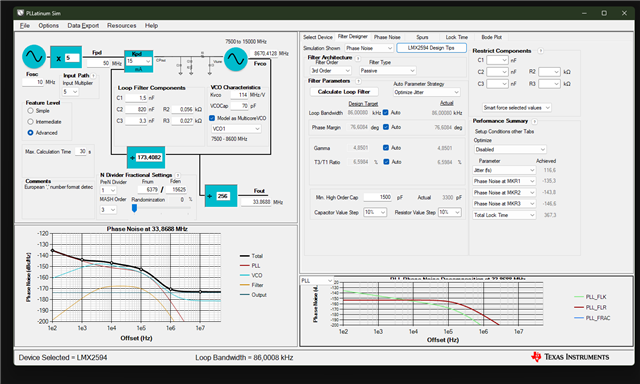

the simulated phase noise in PLLatinum Sim of 116fs cannot be reproduced by measurements. Could you also please share your test setup to verify phase noise measurements?

Thanks and regards

Alex

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

All,

the simulated phase noise in PLLatinum Sim of 116fs cannot be reproduced by measurements. Could you also please share your test setup to verify phase noise measurements?

Thanks and regards

Alex

Hi Alex,

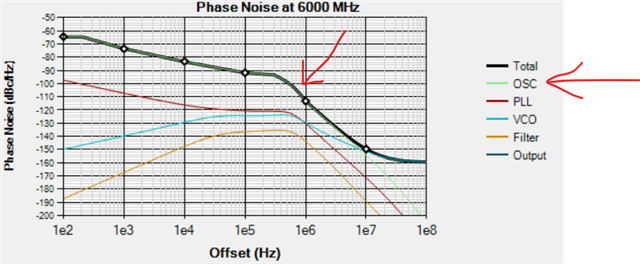

You need to include the phase noise of the reference clock in the simulation.

1. create a text file similar to below, the offset frequencies on the left is in Hz.

10 -75 60 -100 200 -100 1000 -109 10000 -119 100000 -128 300000 -130 500000 -135 1000000 -141

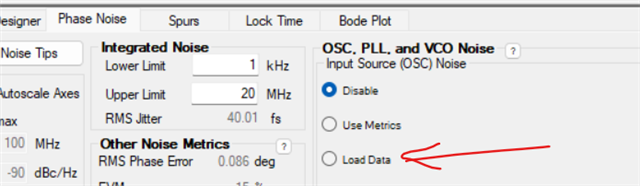

2. load the text file to PLL Sim

Then you can see the phase noise contribution from the reference clock, for example,

The other factor that made the difference between sim and actual is the slew rate of the 10MHz clock. PLL Sim does not take care the effect due to slew rate. PLL likes high slew rate input clock. PLL noise is lower with higher slew rate.

If you have to use 10MHz input clock, you need to use square wave clock such as CMOS or differential clock.

10MHz sine wave clock will hurt PLL noise badly.