Tool/software:

Hello TI Support,

I have a question in regard to the PLL1 and PLL2 of the LMK04828B IC.

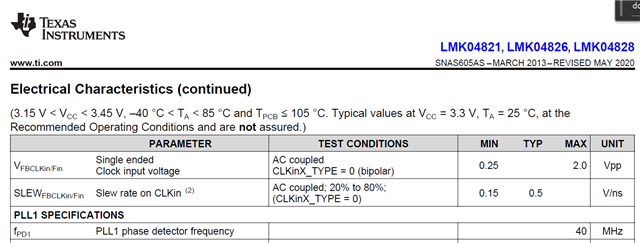

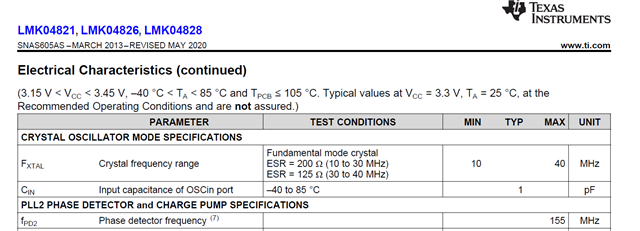

Per the specifications, PLL1 phase detector frequency is spec-ed to be 40 MHz maximum, while PLL2 phase detector frequency is 155 MHz max.

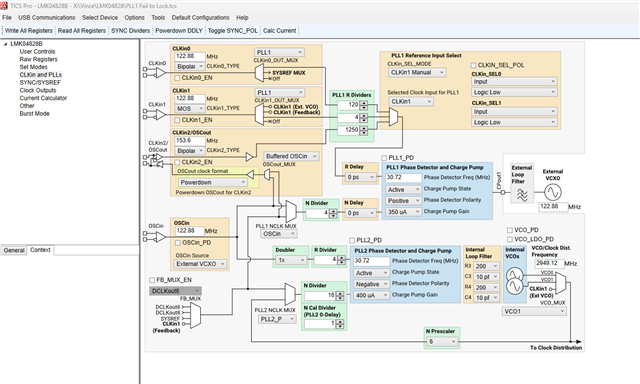

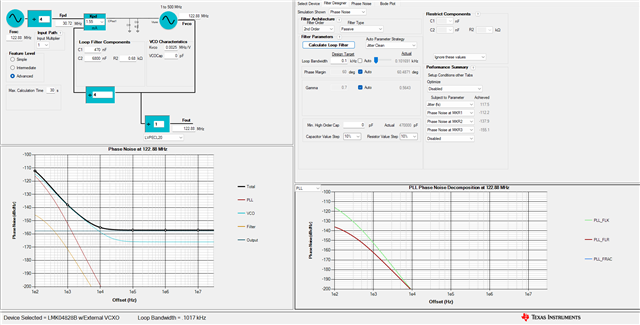

However I only managed to configure them to be outside of spec to obtain the PLL locks (i.e. PLL1 & PLL2 phase detectors @ 122.88 MHz and).

Any other configuration I do to ensure PLL1 and PLL2 detectors to be within spec causes PLL1 to fail to lock.

Can I check if there is an error in the datasheet (or I have an older version) that explains the behavior I am seeing?

Attached are some TIcProSW configuration files that shows both my configuration whereby PLL1, PLL2 locks (refer to "PLL1_PLL2_Locks.tcs") and PLL1 fails to lock (refer to "PLL1 Fail to Lock.tcs").

I am trying to understand where the discrepancies are or there is something I am missing that explains the behavior I am seeing.

Any help you can provide is appreciated.

Thank you.

Regards

TaiPLL1_PLL2_Locks.tcsPLL1 Fail to Lock.tcs