Part Number: LMK1D1204

Tool/software:

Hello,

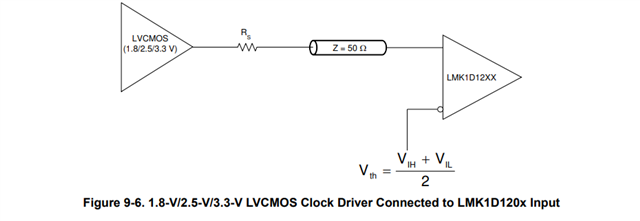

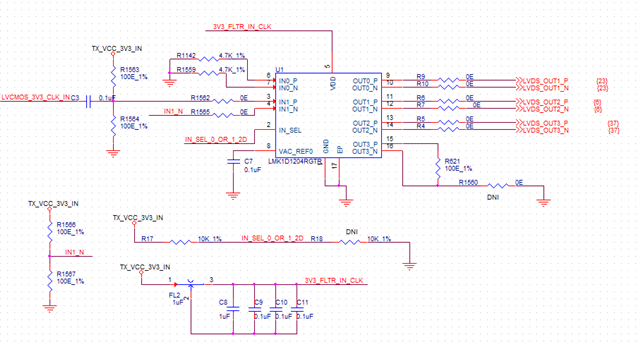

I am using a single-ended LVCMOS clock with a 3.3V amplitude as the input. Please find the attached schematic for reference. I have a few questions regarding the biasing configuration.

Current Setup:

-

The LVCMOS clock signal (3.3V) is AC coupled to the positive input pin, IN0_P.

-

The unused negative input pin, IN0_N, is to be biased at the recommended half-supply voltage of 1.65V.

- Questions:

-

Since the positive input (IN0_P) is AC coupled, do I also need to provide a DC bias to it? If yes, what should be the resistor value?

-

Is a voltage divider required to bias the unused input pin IN1_N at 1.65V, or is another method acceptable?

-

Attached is the schematic above. Please review and let me know if this correct?