Other Parts Discussed in Thread: LMK05318B, LMK04832-SP

Tool/software:

Hi,

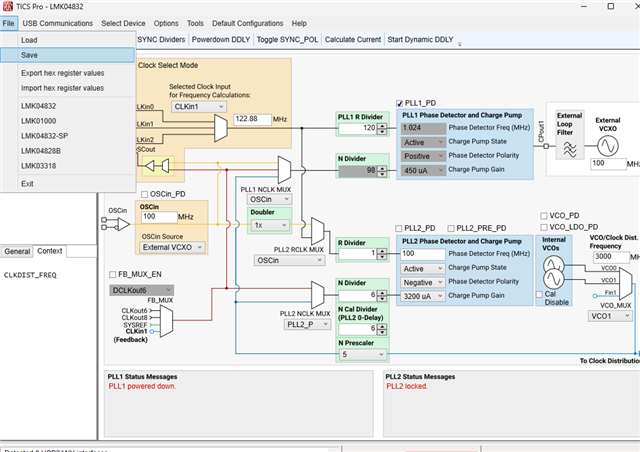

This is Dinesh from iWave Global. I have configured the frequencies based on my requirement but if I save and close it means, some configured frequencies are changed. So I can't save my configured clock file. Attached is the frequencies requirement and please let me know how to save clock file without changing the frequencies. Looking forward to the response.

Regards,

Dinesh