Tool/software:

Hello,

I'm updating a design and I want to connect an unused output from CDCLVP1204 (Vcc = 3.3 V) to a differential clock input on an Altera Agilex 7 FPGA in a 1.2 V bank. It is a 50 MHz clock.

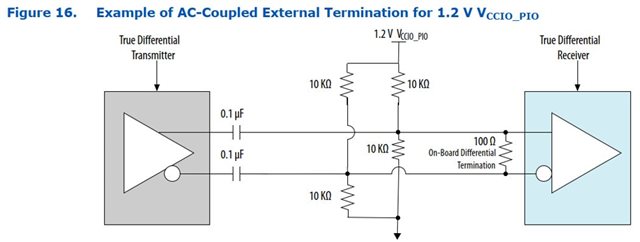

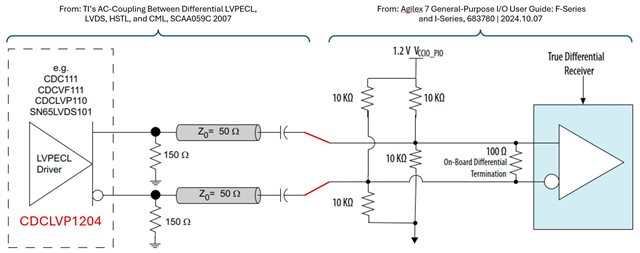

Figure from: Agilex 7 General-Purpose I/O User Guide: F-Series and I-Series, 683780 | 2024.10.07

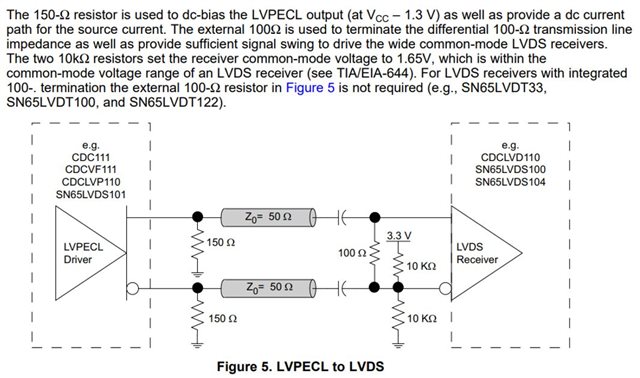

Figure from: TI’s AC-Coupling Between Differential LVPECL, LVDS, HSTL, and CML SCAA059C–2007

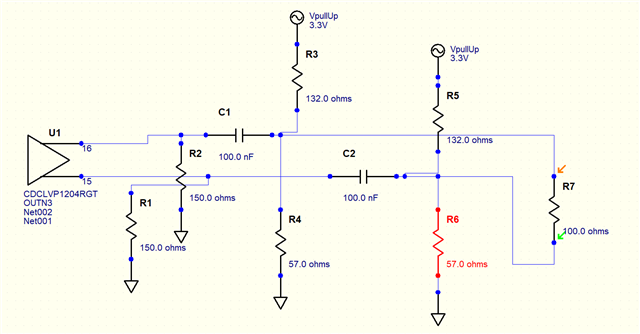

Combined figure:

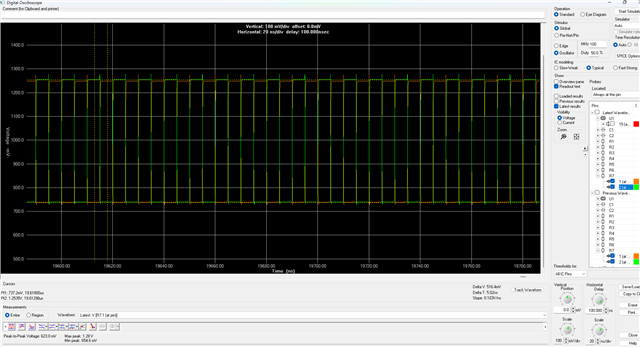

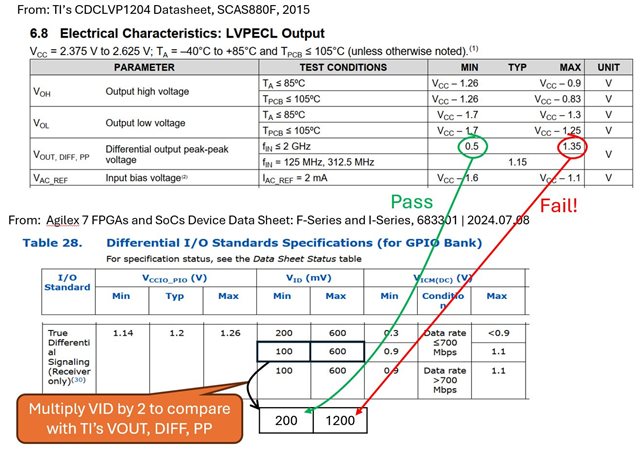

Image showing the numbers don’t work:

Can you provide a recommendation for connecting the two? Perhaps a voltage divider scheme?

Thanks,

Rob