Part Number: LMK04821

Hi all,

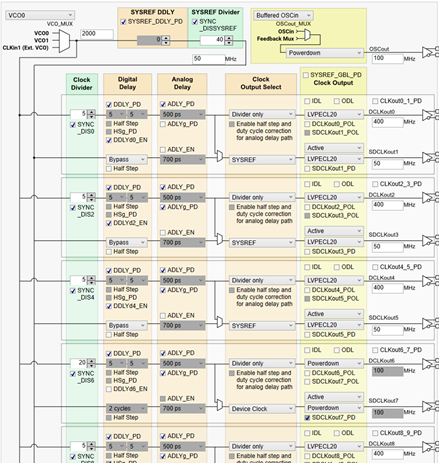

I have problems with the Zero Delay Mode for an LMK04821. We use our own

custom made board, set up all the registers using TICS Pro. Both PLLs lock,

but when I compare the input and output frequency I can see the phase between

the two clock is not always aligned. This happens about 2 out of 5 times

I have attached the register settings.

Ralf