Other Parts Discussed in Thread: AM6421,

Hello, We are using CDCLVC1310 clock buffer in one of our designs which is based on AM6421 processor. While refering to EVM schematic "PROC101C(004)_SCH", we found some hardware circuit related queries for CDCLVC1310 on page# 31. Please refer snapshot along with EVM schematic for your reference:

1) Why did we use voltage devider (R255 & R245) at the output of XO (25MHz - U71)?

2) Why we have used Overdrive (Ac-coupling) mode for a path from XO (25MHz - U71) to Clock buffer (CDCLVC1310RHBR - U70)?

As far as i know, if we are using CMOS output XO (25MHz - U71), it is good to use Bypass mode instead of Overdrive mode. Correct me if i am missing something here. Is there any specific rationale here to use Overdrive (Ac-coupling) mode?

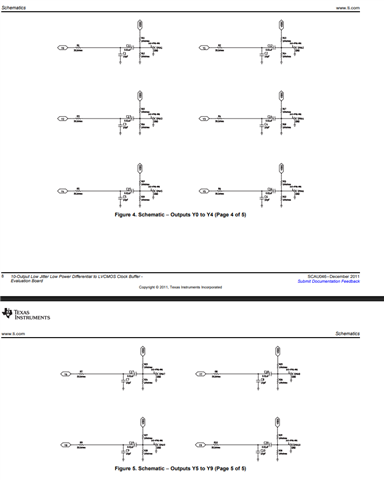

3) At clock buffer output, there are parallel RC dampling networks (C262 & R65 etc.) for Y5 to Y9 only. Why isn't the same is used for Y0 to Y4?

Regards,

Nikhil Jadhav