Hi TIer

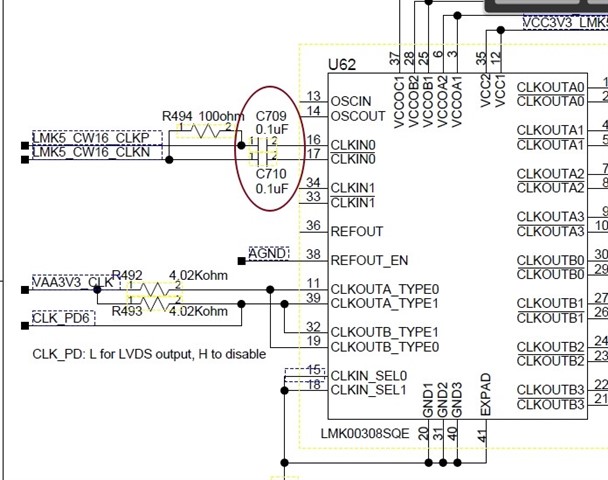

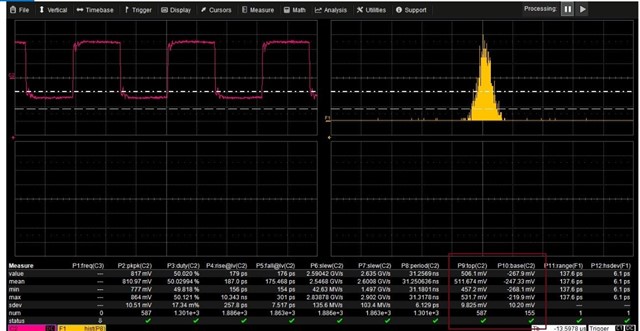

Currently , I have a pair of LVDS to the CLKIN/P0 (16 and 17 pins) of the LMK00308SQE clock chip, measured with a differential probe after the capacitance (C709_2/C710_2) was straightened, and found that the Vcm was not at 0v level, with bias, See Figure

The bias is about 0.25V, do you think this is a problem? Is it related to the VCMD parameter in the datasheet? Please give me some advice Thank you

add the waveform

add the waveform