Part Number: LMKDB1202

Hi,

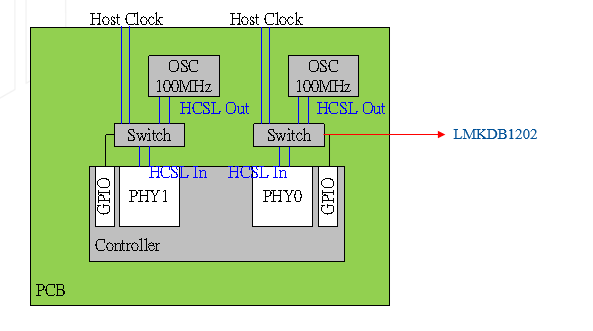

We needs to support switching between SRIS and CC modes at the system level.

The oscillator is 100 MHz with HCSL output, and the PHY uses a 100 MHz HCSL input.

Would you please review below application and shcematic? thanks!

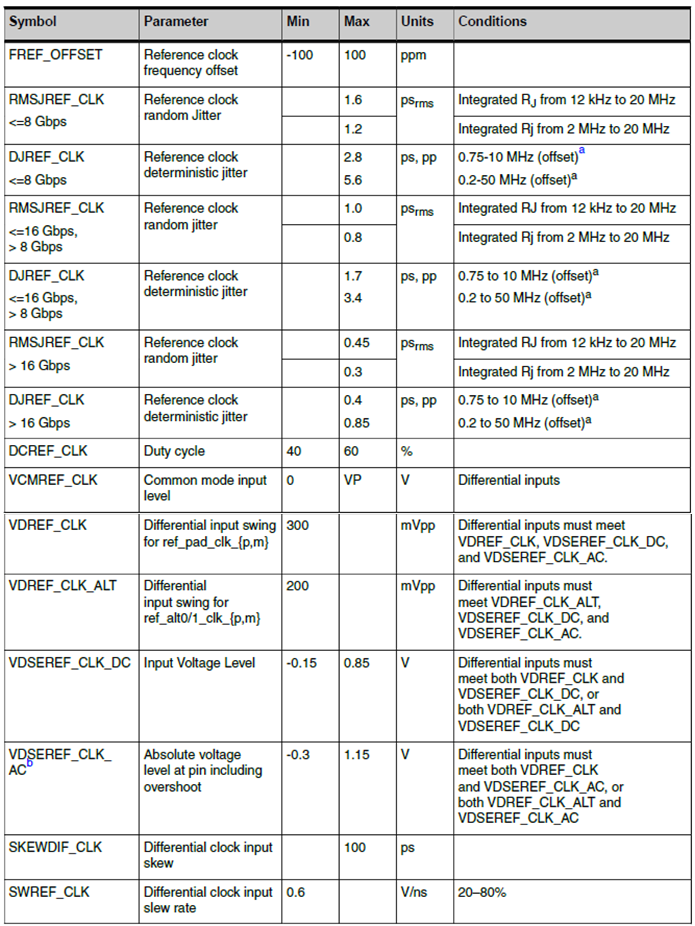

100MHz OSC Output Spec.

PCIe Phy RefCLK Input Spec

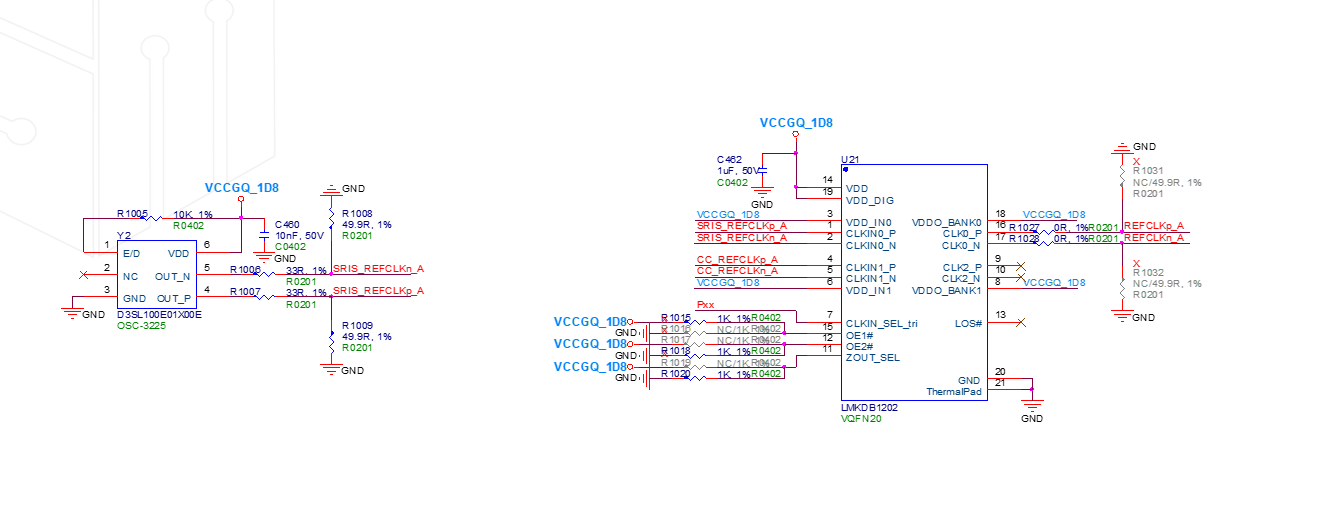

Schematic:

Jeff