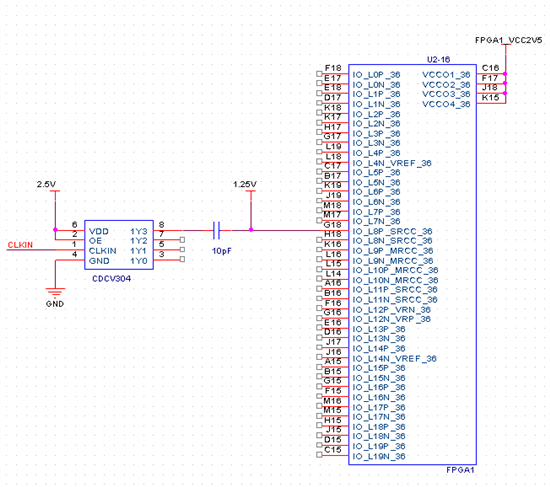

The CDCV304 clock output pins (Y0, Y1, Y2, Y3) if a pair is unused can i leave this pins unconnected or should I terminate it? If so what is the recommended termination scheme?

Is there any performance degradation if I leave the unused pin no connect?