Hi:

I'm using cdce62005 with spartan6 FPGA, cdce62005 works as a jitter cleaner for the gtp 125MHz reference clock, it works fine. I can get a stable recovered clock from the gtp. Now I want to switch the clock source of the cdce62005 from a local 125MHz clock to the recovered 125MHz clock, after switching for some micro seconds, cdce62005 loses lock. The only clock source for me is sec_ref, so I implement a internal mux to do the switch job.

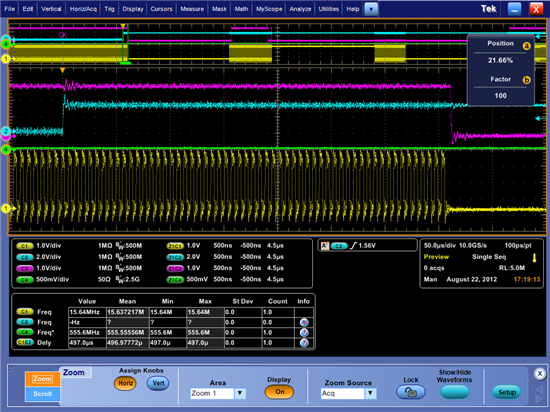

The clock switch happened at the rising edge of the blue channel, the red channel represents the cdce62005 lock signal, the yellow one is the aux_out which is 1/8 of the reference clock(sec_ref) .From the waveform I didn't see any obvious change before and after the clock switching, I can't understand why cdce62005 can't lock at the new clock.

At my last design I used a si5368 as a jitter cleaner and there is a Hitless switching function which makes the switch quite easy, is there any similar function in cdce62005 ?

My register setting is as below: reg8 is actually reg6 , I use it to initial a calibration.

#define reg0 0xe9040300

#define reg1 0x68040321

#define reg2 0xe9040302

#define reg3 0xe9040203

#define reg4 0x68040334

#define reg5 0x500c0eb5

#define reg6 0xb05e0366

#define reg7 0xbd887447

#define reg8 0x945e0366

Thank you very much in advance for your kindly help.