From the datasheet of the CDCM7005, I have some qustions i can not understand.

The dadasheet said that ''TheCDCM7005is ahigh-performance,low phasenoise and low skew clock synchronizer that synchronizesa VCXO(voltage controlledcrystal oscillator)or VCO(voltage controlledoscillator)frequency to one of the two reference clocks.The programmable pre-divider M and the feedback-dividers N and P give a high flexibility to the frequency ratio ofthe reference clock to VC(X)O: • VC(X)O_IN/ PRI_REF=(N xP)/ M or • VC(X)O_IN/ SEC_REF=(N xP)/ M VC(X)O_IN clock operates up to 2.2GHz.Through the selection of external VC(X)O and loop filter components, the PLL loop bandwidth and damping factor can be adjust to meet different system requirements.''

1.How to calculate the output frequency of the CDCM7005 ? How much the maximum output frequency ?

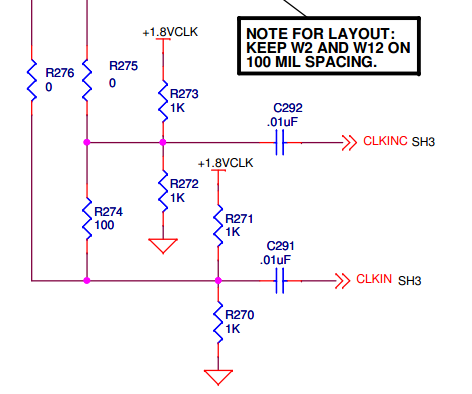

2.If i do not provide the clock to the VC(X)O, VC(X)O_IN (pins E1,D1) ,can the chip work normally ? (from the DAC5670_EVM)

3.Do the P divider supply the function of phase shift and the divider function which is simliar to the M divider ?