Hi,

We have designed a board with two C6678 DSPs and we use two CDCE62005 clock generators.

Each clock generator has a separate 25MHz external oscillator.

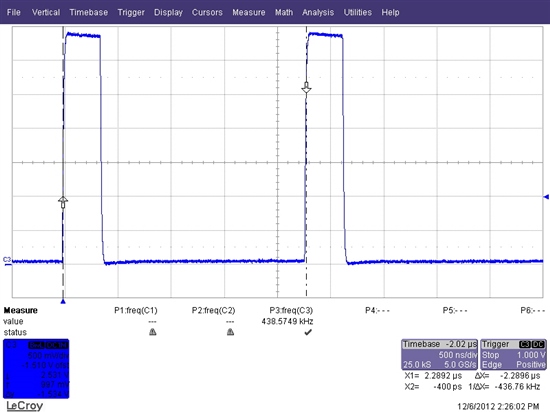

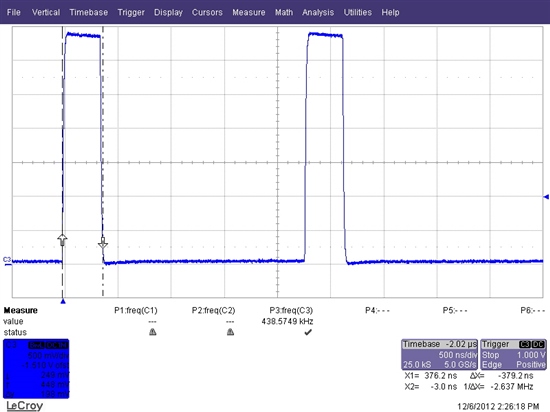

The problem is that both devices does not have PLL lock. This signal toggles but id does not achieve PLL lock.

CLK1 has one output of 100MHz and four outputs of 250MHz (all outputs are LVDS).

CLK2 has all five outputs of 100MHz (all outputs are LVDS).

Here are the registers:

CLK1:

0 e9 85 ff 20

1 e9 85 ff 21

2 e9 07 ff 02

3 e9 85 ff 03

4 e9 85 ff 14

5 10 00 0b 35

6 00 fe 03 e6 // Reg. 6 bit 27 is '0' for start-up PLL calibration mode

7 fd ff ff f7

CLK2:

0 e9 07 ff 20

1 e9 07 ff 21

2 e9 07 ff 02

3 e9 07 ff 03

4 e9 07 ff 14

5 10 00 0b 35

6 00 fe 03 e6 // Reg. 6 bit 27 is '0' for start-up PLL calibration mode

7 fd ff ff f7

Please advise!