Other Parts Discussed in Thread: CDCE62005

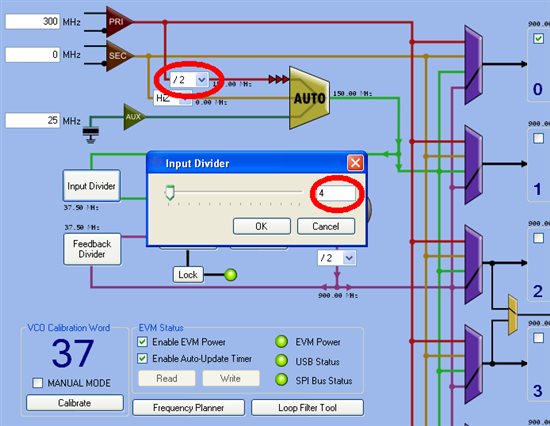

Setup with Fout= Fin. For Fin=297MHz, calibrate function returns calibrate word=1 and output is not at correct frequency. Is this a known issue?

When I toggle "enable evm power" check box in GUI correct output is observed.