Sir:

I need do a design with 4 ADS5474 to implement a interleaved ADCs, in which the sampling rate is 1.3G and each ADC works in 325M.

Now I have two clock schemes:

(1)One is used the dual PLL LMK04816, which can produce the clock with jitter of 100+ fs.

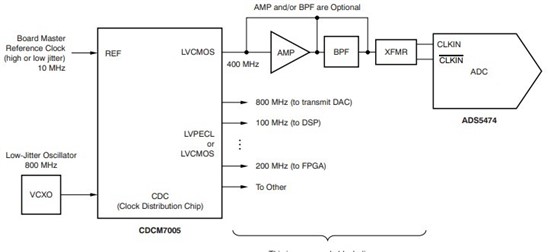

(2)The second is the recommendation of datasheet of ADS5474. In this method, I want use PLL to generate 325M clock and use BPF to filter the clock. Then, I use the XFMR to generate the clocks of 0, 90, 180, 270 degree phase ***. The below picture is the recommendation configuration from datasheet ADS5474.

I want to know, which method can get better clock? I need a sampling clock with minimum phase noise.

Is there any other better clock solution that is suitable for my application?

Thank you!

best wishes

Jacky