Hello Sir,

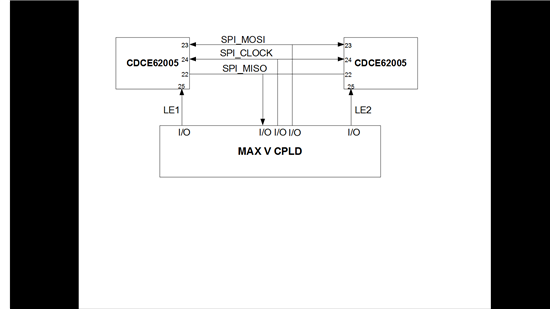

We are using 2nos of clock synthesizer IC CDCE62005 in our design. The SPI interface signals are connected to MAX V CPLD I/O pins as shown in the image

My Query :

In the datasheet of CDCE62005, it is mentioned that the typical output load capacitance value for MISO is 3 pF. The CPLD I/O pins have input capacitance of 5 pF. Is this value 3 pF a typo error?

And in my design, the MISO of both ICs drive same I/O. Is there any issue in this type of connection, in spite of these capacitance value mis match ? (NOTE : I have provided Pull up for the MISO at the CPLD side).

Please clarify on this.

Regards,

Vijetha