I've been working with the LMK03033C, but I haven't been able to lock it, I have been using 20 and 40 Mhz clock inputs by adjusting R divider to be at (200,400) respectively (Targeting a 100 khz at the phase comparator), I am able to see the Rdivider frequency through PLL_MUX=11, but not the Ndivider, LMK is being driven single ended, AC coupled by .1 uF capacitors. I have reviewed http://e2e.ti.com/support/clocks/f/48/t/248734.aspx?pi196085=1, and tried to visualize the data stream coming into the device, and it seams correct, each clock cycle lasts at least 250 ns, while LE has been adjusted to 1 us, to ensure correctness.

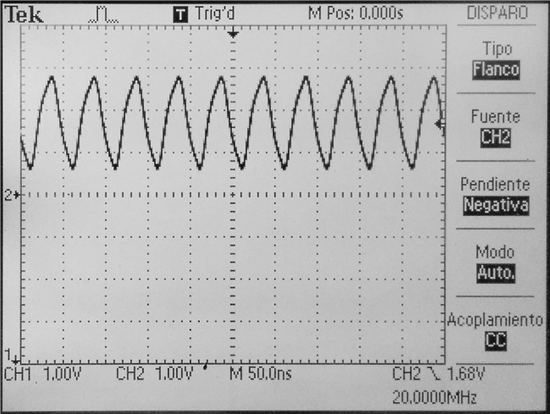

I have also checked the Voltage signal, it is at 3.4V with a 20-30 mv ripple. Upon configuring the LMK it always seems that the internal VCO frequency is at 2230 Mhz, since the VCO divider is configured at 3, and individual clock lines are divided by 234. At lines 4, and 7 the output is 2.2258;hz, I can adjust the divisors and see that there is a frequency change on those lines. I am able to test the Reset command (since the clock lines become off), the R0 through R7 (due to the clock dividers), am also able to test R9 since Vboost amplfies the signal comming out of lines 4 and 7. Further more I can configure PLL_MUX located at R14, since I can see through the LD pin the Rdivisor frequency (around 50.003 in my case), but I'm unable to see the Ndivider output.

I repeated the before mentioned procedures on 2 mounted PCBs with the same result, Could I be missing something here?

And Of course my programming sequence

R0 0x80000100 =initial Reset

R0 0x00000100 =Disable Line 0

R1 0x00000101=Disable Line 1

R2 0x00000102=Disable Line 2

R3 0x00000103=Disable Line 3

R4 0x0003A704=Enable Line 4, Clock Divider=334, Clock Mux=divided

R5 0x00000105=Disable Line 4

R6 0x00000106=Disable Line 6

R4 0x0003A707=Enable Line 7, Clock Divider=334, Clock Mux=divided

R8 0x10000908=Calibration

R9 0xA0032A09=Vbust=1

R11 0x0082000B=Div4=0

R13 0x0285800D= .OSCin_FREQ=20 VCO_C3_C4_LF=0; VCO_R3_LF=0; VCO_R4_LF=0;

R14 0x0890C80E = PLL_R=200, EN_CLKout_Global=1; EN_Fout=0; PLL_MUX=9

R15 0x0C18380F= PLL_CP_GAIN=0;VCO_DIV=3; PLL_N=6200