Hello

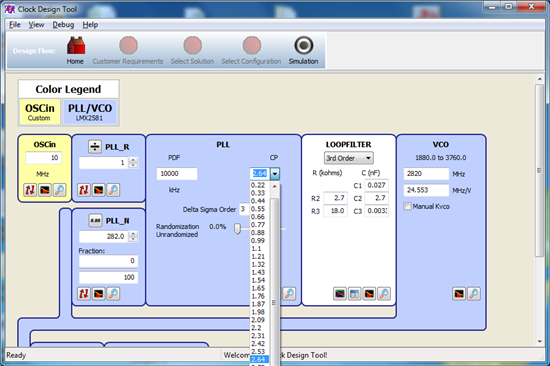

I would like to know the function of the Fastlock in the LMX2581.

1. How to decide the value of the R2pLF in the table 9 Fast lock configuration of the Data

sheet ?

- Although the table give user way of calculating K, it is difficult for beginner. Please let me

have an example for calculating process.

2. How much Lock time it has between Normal mode and Fastlock Mode

Thanks and Best Regards