Hi

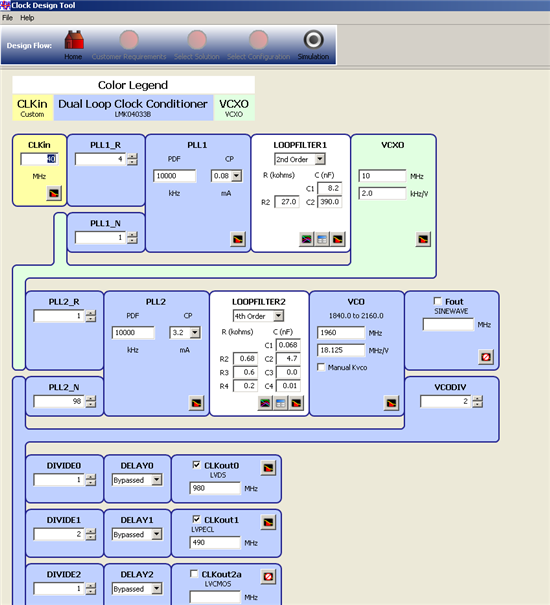

About the lmk04033b I want to use both pll1 and pll2 section of device and for pll1 section I use 40 MHz VCXO for CLKin0 port and left CLKin1 port floating. According to datasheet and guidance of clock design tool I will use 10 MHz VCXO for OSCin port. is this design applicable or not

regards