I use CDCM6208 on my board.

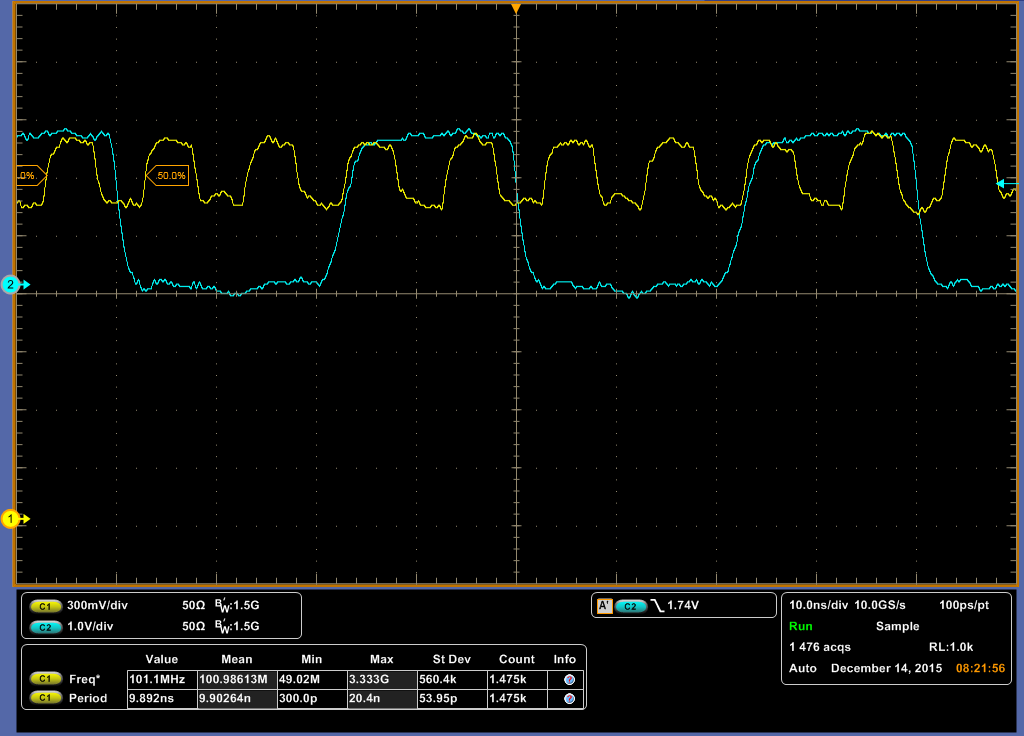

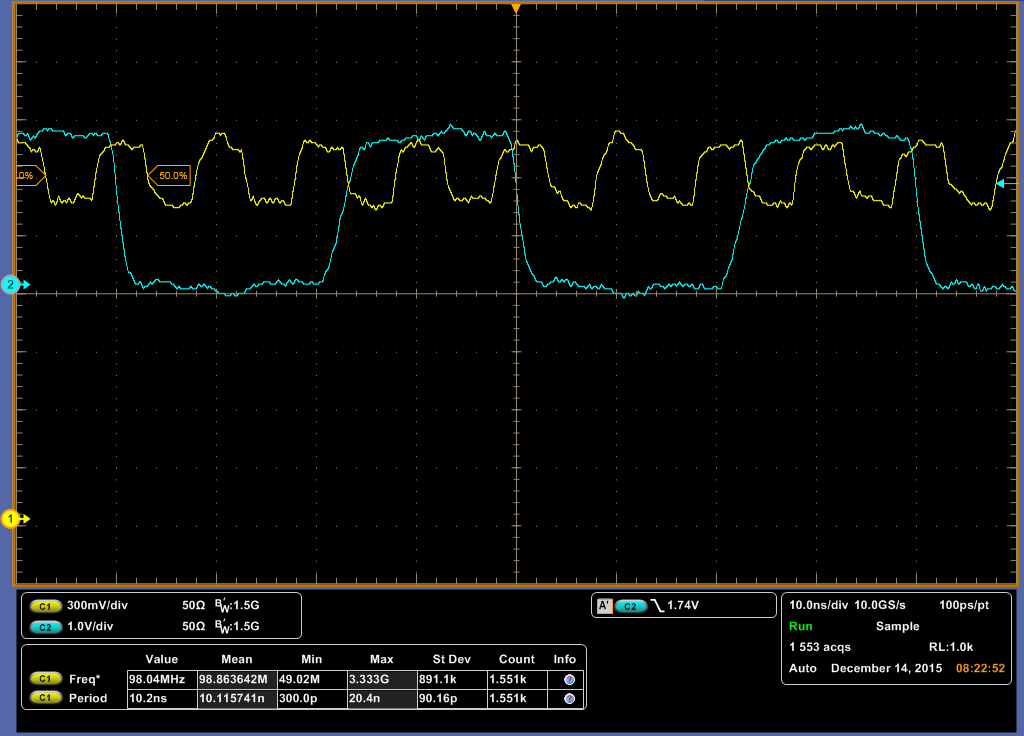

When I measure the phase difference between input_ref_clk(25MHz, from a crystal) and output_clk(100MHz), I found that the phase difference is always random when I powered on the board every time.

In my understand, the PLL should make the phase of output_clk equal to the input_ref_clk, so that is Phase Lock Loop!

But why the phase difference is not the same value when I power on the board every time?