Hello,

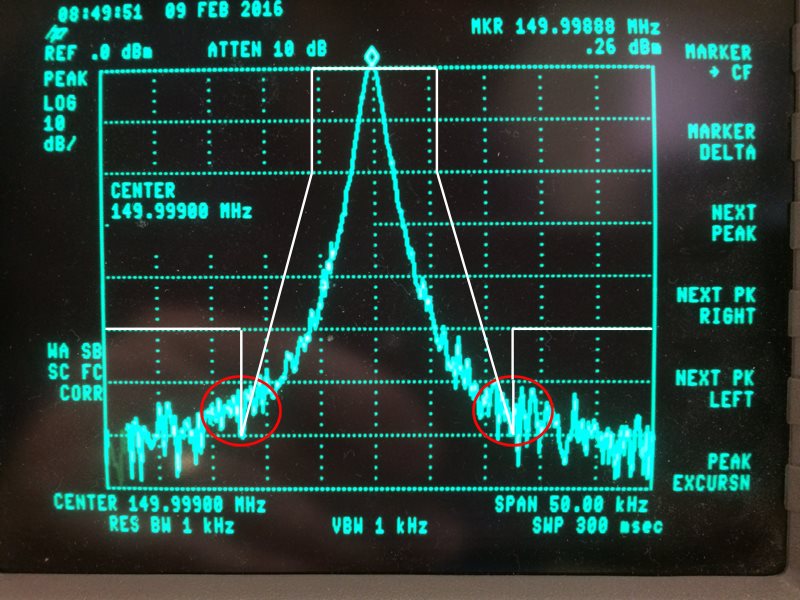

We're using the LMX2571 as a synthesizer for an FCC Part 90 application and for the most part, it's working well. However, we have noise that we need to reduce. In my photo, I've marked FCC Emission Mask D in white and circled the emission area of concern in red. This spectrograph was generated using the TI EVM board and loaded using CodeLoader (nice tool, by the way). Modulation was turned off. We get very similar results using the board we designed using the LMX2571. Our TCXO, is a Connor Winfield DV75D TCXO with jitter < 1ps (like the EVM). Our loop filter design on pin 25 (CPout) is the same as that used on the EVM board.

What is likely to be the source of this noise? Loop filter? VCO noise? Is 1ps jitter too high?

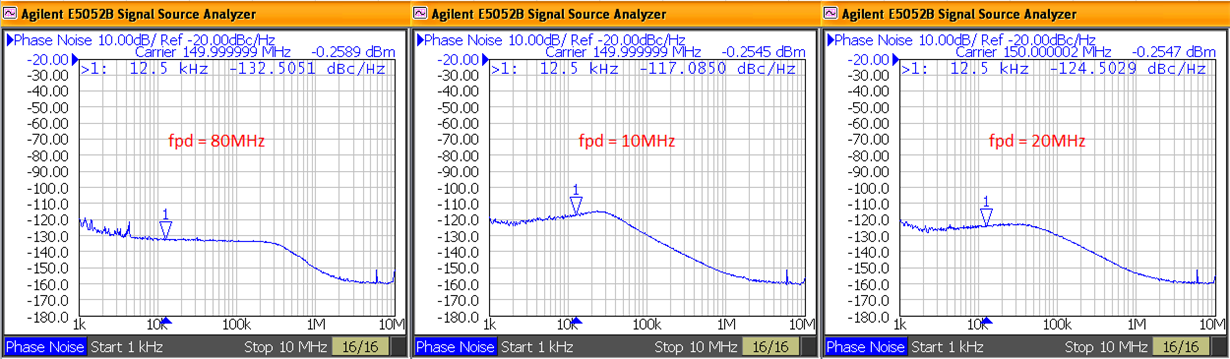

We have adjusted the phase detector frequency up from our original 10mHz value but there was no noticeable noise reduction. We have also adjusted the internal LFR3, and LFR4 values as well as the charge pump current and gain, still with no reduction in noise. If I need to change the LF bandwidth, I would very much appreciate help in selecting values or a pointer to app notes that specifically call out the math for component selection.

Thanks!

Steve