HI,

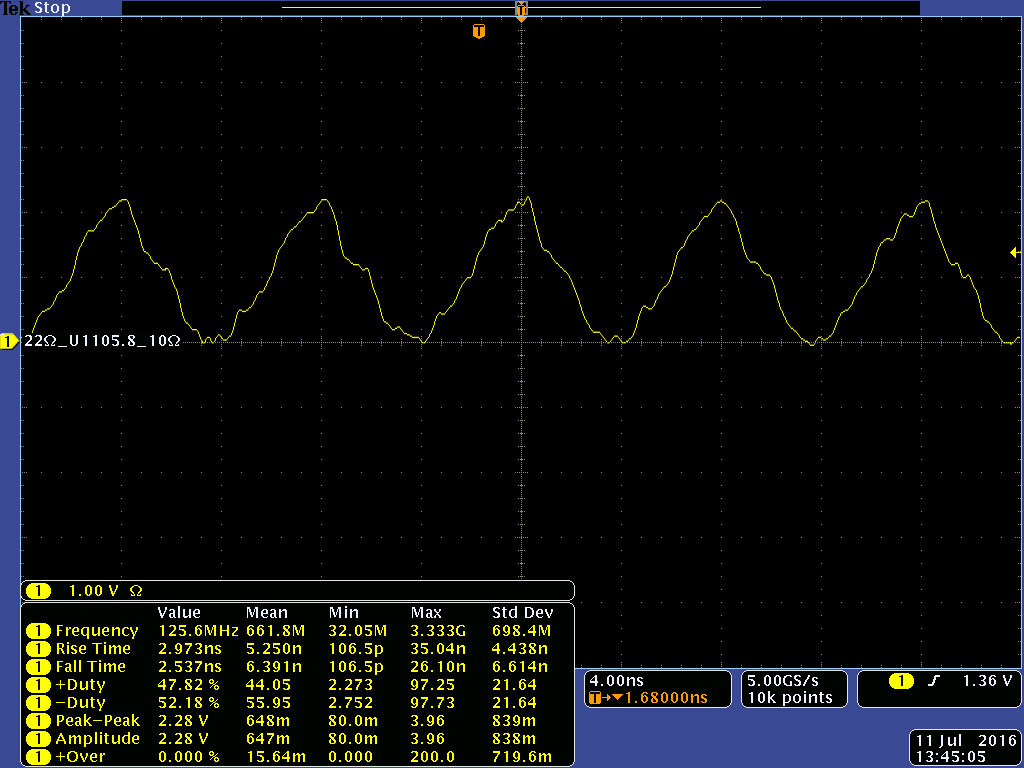

We are using a clock buffer (PN: CDCLVC1102PW) with operating voltage 2.5V and input clock assigned 125MHz from clock synthesizer(PN: XR81101) output. as per datasheet output parameter rise and fall time should be 0.3ns to 1.2ns.

but, observed that,

first, I captured waveform at clock buffer input terminal and parameters are with in specified range only. second, I captured waveform at buffer output and looks rise and fall parameters are changed a lot compared with datasheet parameter.

Oscilloscope bandwidth is 1GHz and sampling rate is 4GSps and differential probe I used and bandwidth is 1.5GHZ

Please see captured waveform and schematic and help on this issue and need to solve immediately.