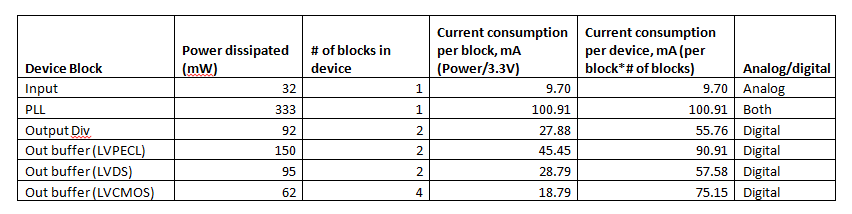

How is the power usage distributed between the digital and analog rails on this chip? I would assume that the analog supply needs to supply the majority of the ~300mA needed, but I can't find anything on the datasheet that specifies this.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.