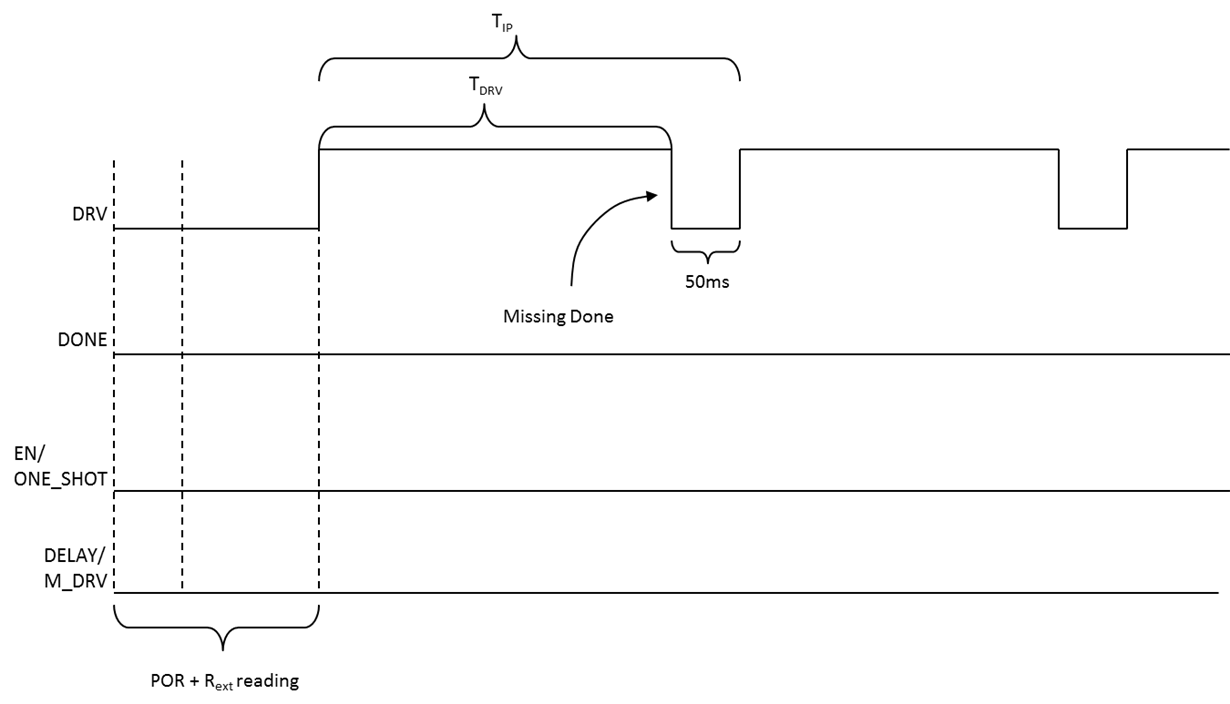

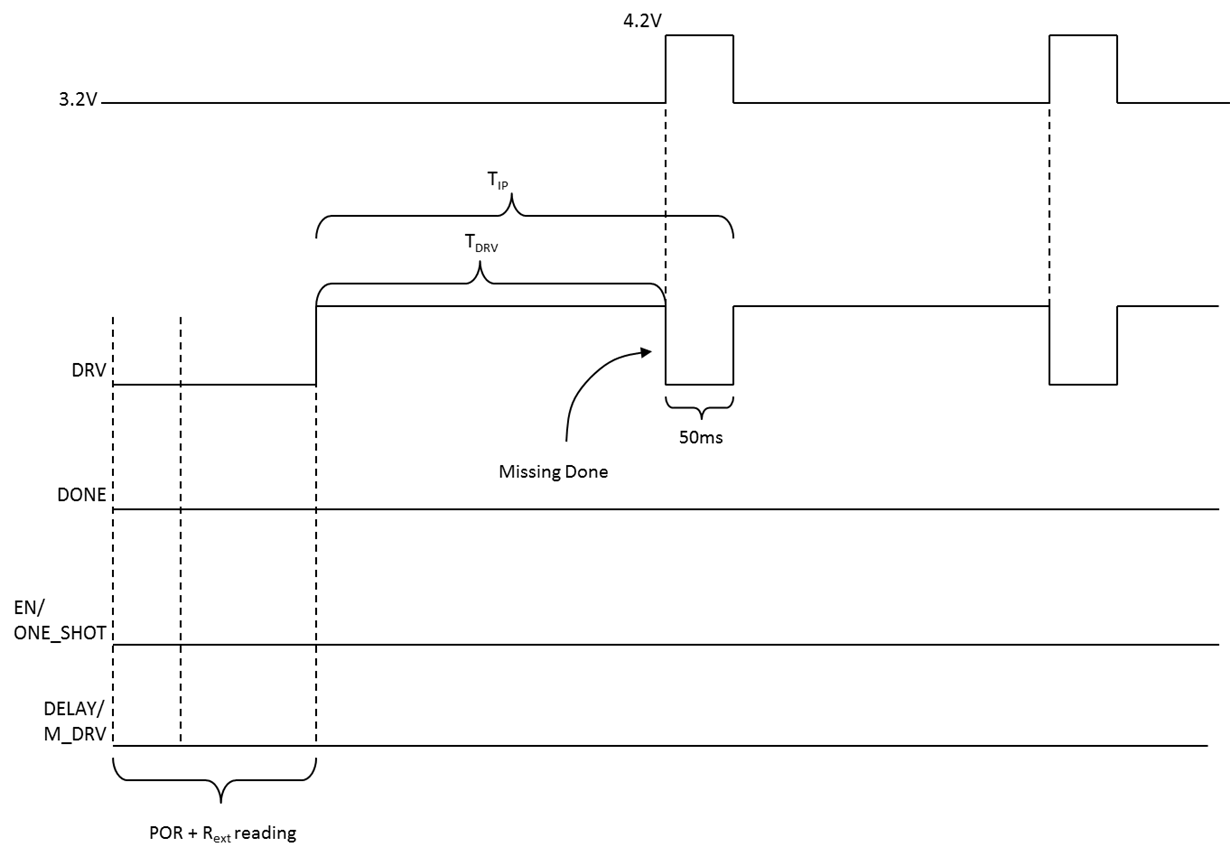

If VDD jumps from about 3.2V to about 4.2V It looks like the TPL5111 treats this like a power-on event and after about 80ms asserts the DRV signal.

Is this known behavior? What are my options for getting around it?

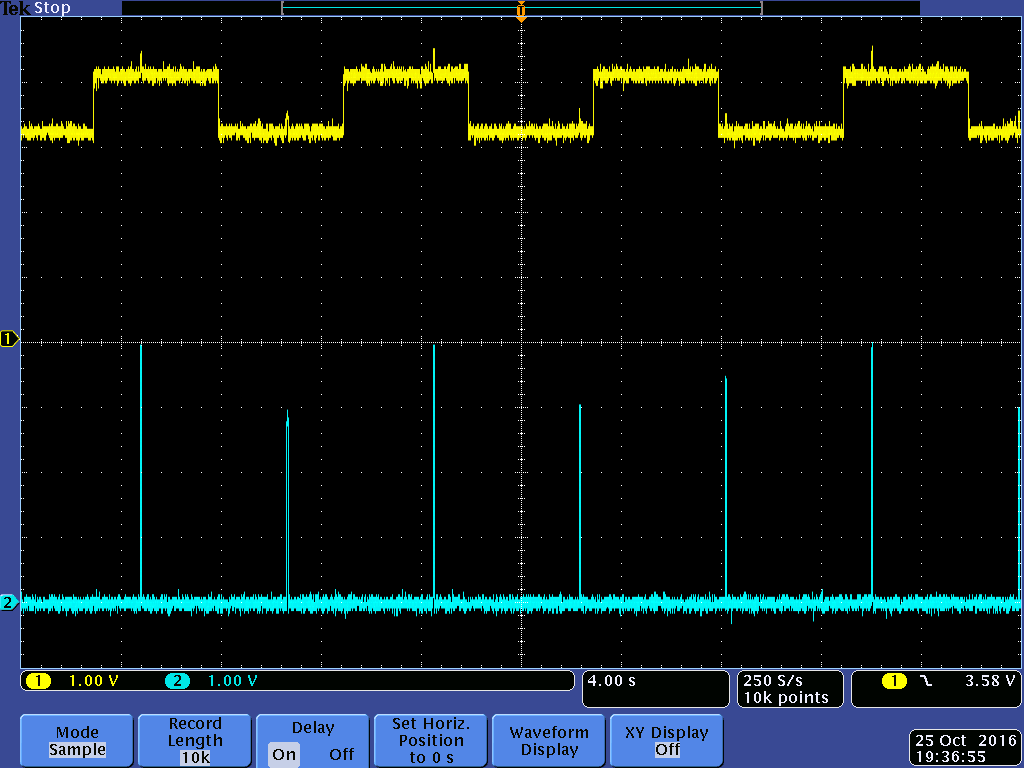

In the oscilloscope screenshots below:

trace 1 is pin 1 (VDD)

trace 2 is pin 5 (DRVn)

pins 2 (GND), 4 (DONE), and 6 (EN/ONE_SHOT) are shorted to ground

pin 3 has a 10k pulldown to ground.