Hello,

While using a custome prototype board. I am unable to have a lock on the clock while having a reference 48Mhz clock and a 48Mhz output unless I am using Cycle Slip Lock Window. However it doesn't seem to be locking as I am not able to see the lock between the input clock and the CDC output clock.

I am using the passive loop capacitors and resistor values that are given as example in the datasheet.

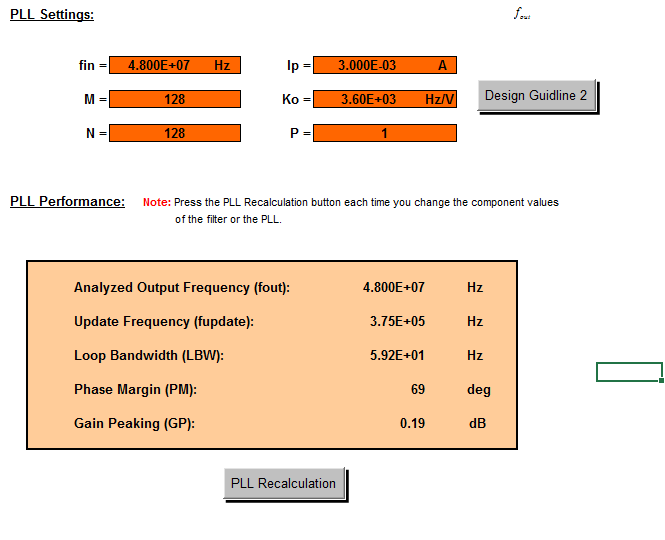

The values that I used in the PLL are the ones shown bellow:

LBW seems a bit low but my guess is that shouldn't be a problem.

I am using the a 48Mhz VCXO with:

Control Voltage Tuning Slope - 40 ~ 75 ppm/V

BW - 10 kHz

The settings that I am using for the CDCM7005 configuration are the following:

word 0: 0x4007F1FC

word 1: 0x28000001

word 2: 0x500000F2

word 3: 0x0000024B

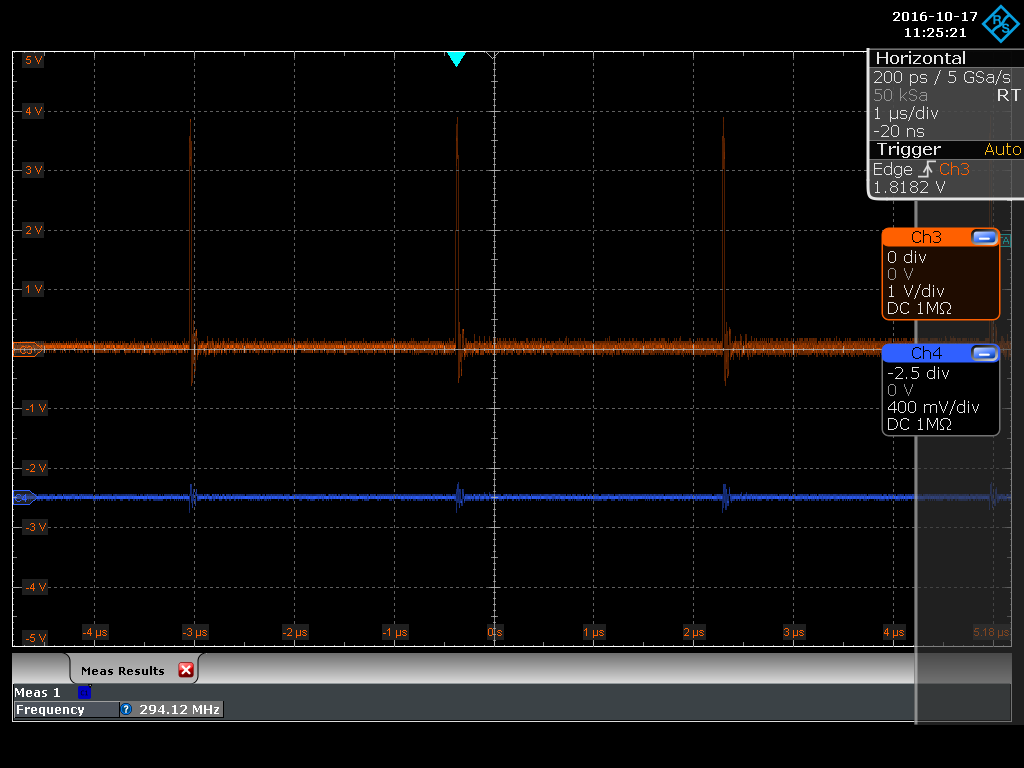

Using the test configuration to see the internal clocks I don't see the VCXO clock (in blue bellow)

Ch3 (orange): STATUS REF

Ch4 (blue): VCXO STATUS

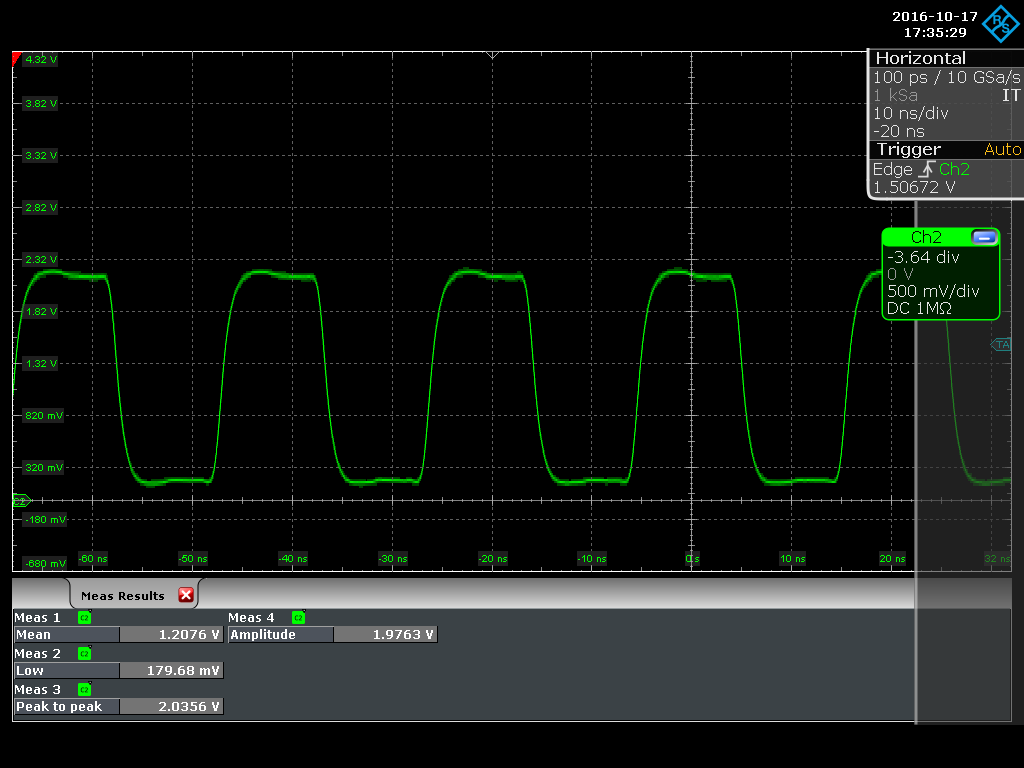

I seem to have the right values for a LVCMOS VCXO. The conditioning circuit is bellow as well as the measured VCXO input in the CDC

The input VCXO input on the CDC is the following:

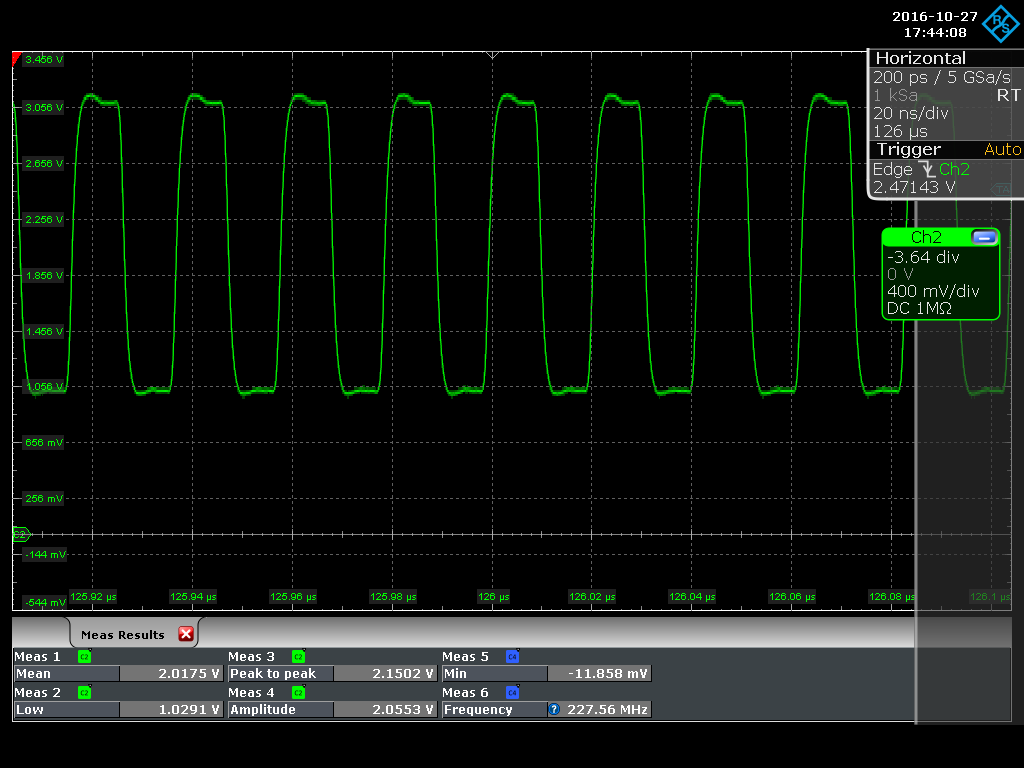

The outputs are toggling at the correct frequency although there is no lock.

Thank you