Hello,

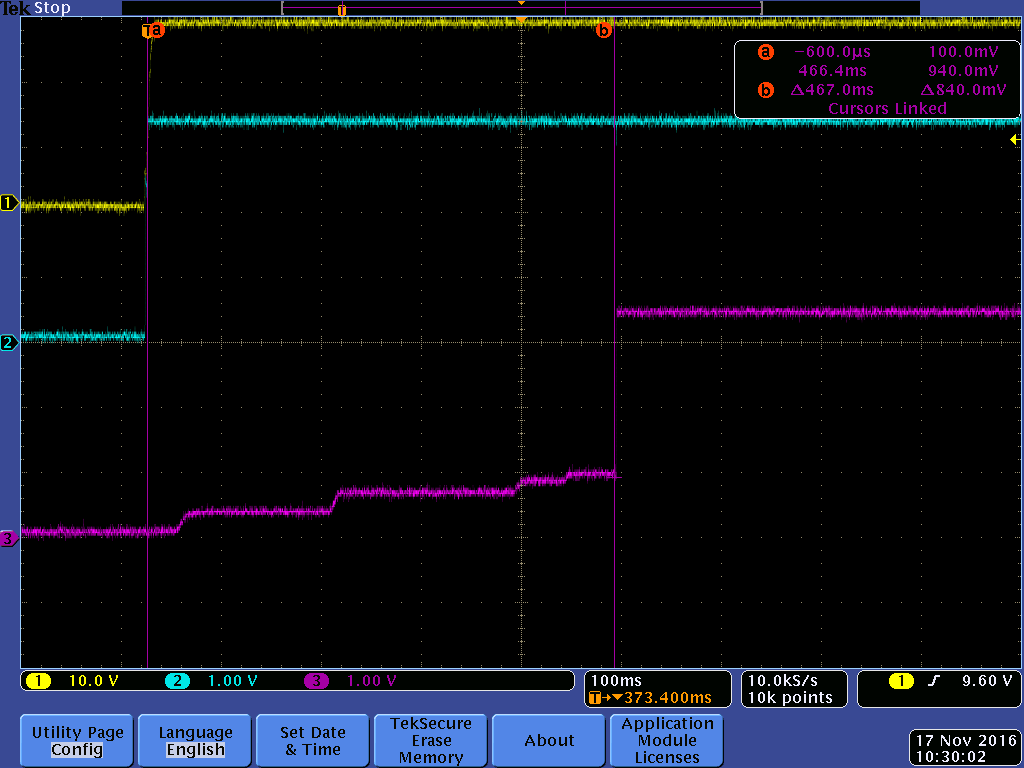

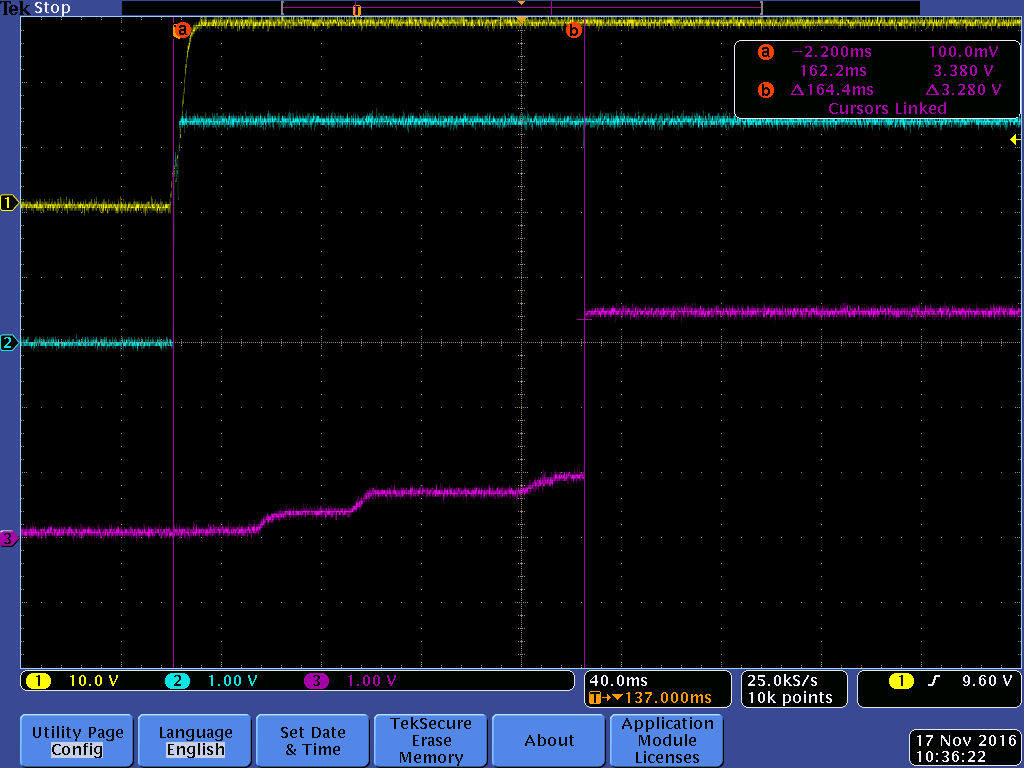

We have currently implemented the CDCE62005 in two different ways. One with the Power Down pin tied to VCC_OUT (in this configuration the synthesizer becoming unlocked around 30% of the time), whereas in another configuration the power down pin is connected to the FPGA (the pin is pulled down during power up and then driven high once the FPGA is configured) they don’t see the issue (I can provide schematics if you connect with me on e2e or I can also email them).

Seeing as one of our TI reference designs (TSW6011 EVM) also ties Power Down to VCC_OUT, I’m wondering if issues have ever been seen with that design or if maybe their problem stems from something else?

I interfaced previously on this with another person from the clocking team and they asked us to add 0.1uF of capacitance on the PDN to solve the issue. In the setup with PDN tied to VCC_OUT, we noticed that VCC_OUT is a 3.3V regulated supply with already 770nF of capacitance. We wanted to ask if we could try an LC circuit to isolate the capacitance in efforts to hold PDN low, longer? In table 4 of the datasheet it mentions after the power supply reaches approx. 2.35V, the contents of the EEPROM are copied into the Device Registers. Is this the voltage level the PDN considers a low-to-high transition?

Do you have any other comments on this or have you ever heard of this occurring before?